# VT6122

## **Gigabit Ethernet Controller**

DATASHEET

Revision 1.6 May 21, 2004

VIA Networking Technologies, Inc.

## **Copyright Notice:**

Copyright @ 2003, 2004 by VIA Networking Technologies, Incorporated. All Rights Reserved.

No part of this document may be reproduced, transmitted, transcribed, stored in a retrieval system, or translated into any language, in any form or by any means, electronic, mechanical, magnetic, optical, chemical, manual or otherwise without the prior written permission of VIA Networking Technologies, Incorporated.

VT6122 may only be used to identify a product of VIA Networking Technologies.

All trademarks are the properties of their respective owners.

## **Disclaimer Notice:**

No license is granted, implied or otherwise, under any patent or patent rights of VIA Networking Technologies Inc. VIA Networking Technologies Inc. makes no warranties, implied or otherwise, in regard to this document and to the products described in this document. The information provided by this document is believed to be accurate and reliable as of the publication date of this document. However, VIA Networking Technologies Inc. assumes no responsibility for any errors in this document. Furthermore, VIA Networking Technologies Inc. assumes no responsibility for the use or misuse of the information in this document and for any patent infringements that may arise from the use of this document. The information within this document are subject to change at any time, without notice and without obligation to notify any person of such change.

## Offices:

USA Office: 940 Mission Court Fremont, CA 94539

USA Tel: (510) 683-3300 Fax: (510) 683-3301 -or- (510) 687-4654 Web: www.vntek.com

#### Taipei Office:

533 Chung-Cheng Road, 8F Hsin-Tien, Taipei 231 Taiwan Tel: +886 (2) 2218-2078 Fax: +886 (2) 2219-8461 Web: www.vntek.com.tw

| <b>Document Release</b> | Date       | Revision                                                                                                                                            | Initials |

|-------------------------|------------|-----------------------------------------------------------------------------------------------------------------------------------------------------|----------|

| 1.0                     | 2003-10-13 | Initial release                                                                                                                                     | SHC      |

| 1.1                     | 2003-12-12 | Modified values in Table 22 "Absolute Maximum Ratings" and in Table 23 "DC Specifications"<br>Added Table 24 "Current Consumption"                  | SHC      |

| 1.2                     | 2003-12-17 | Modified Table 22 "Absolute Maximum Ratings"                                                                                                        | SHC      |

| 1.3                     | 2003-12-29 | Modified Table 22 "Absolute Maximum Ratings"                                                                                                        | SHC      |

| 1.4                     | 2004-02-04 | Revised the description of Pin 74, VEESEL                                                                                                           | SHC      |

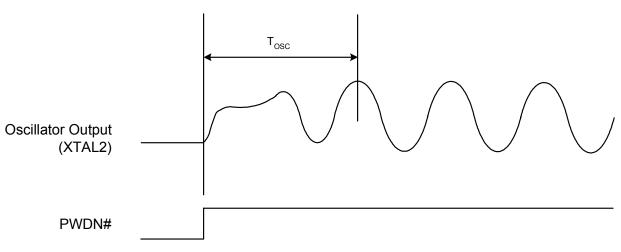

| 1.5                     | 2004-04-16 | Added product information markings and descriptions to the diagram in Figure 16, 128-Pin EP-LQFP Package, in the Mechanical Specifications section. | SHC      |

| 1.6                     | 2004-05-21 | Modified Table 16 "LED Select."                                                                                                                     | SHC      |

## **REVISION HISTORY**

1

## TABLE OF CONTENTS

| REVISION HISTORY                                                                                                   | III |

|--------------------------------------------------------------------------------------------------------------------|-----|

| TABLE OF CONTENTS                                                                                                  | IV  |

| LIST OF FIGURES                                                                                                    | VI  |

| LIST OF TABLES                                                                                                     | VI  |

| PRODUCT FEATURES                                                                                                   |     |

| OVERVIEW                                                                                                           |     |

| PINOUT                                                                                                             |     |

| REGISTERS                                                                                                          |     |

| REGISTER MAP TABLES                                                                                                |     |

| PCI Configuration Space                                                                                            |     |

| MAC Registers Mapping Table                                                                                        |     |

| MII Register Mapping Table                                                                                         |     |

| REGISTER DESCRIPTION                                                                                               |     |

| MAC Registers                                                                                                      |     |

| FIFO Test Registers (Offset 67h~ 60h/ 6Ah 6Bh)                                                                     |     |

| CAM Control Registers (Offset 69h~ 68h)                                                                            |     |

| MII Management Port Control Status Registers (Offset 73h ~ 6Ch)                                                    |     |

| Software Timer Registers (Offset 77h ~ 74h)                                                                        |     |

| Chip Configuration Registers (Offset 7Fh ~ 78h)                                                                    |     |

| MIB Counter Control and Status Registers (Offset 84h, 8Bh ~ 88h)<br>Flash ROM Control Registers (Offset 91h ~ 8Ch) |     |

| EEPROM Control Registers (Offset 97h ~ 92h)                                                                        |     |

| Jumper Strapping Status Registers (Offset 9Bh~ 98h)                                                                |     |

| Wake On Lan Registers                                                                                              |     |

| MII Registers                                                                                                      |     |

| FUNCTIONAL DESCRIPTION                                                                                             |     |

| POWER UP RESET                                                                                                     |     |

| Host Bus Interface Control Logic                                                                                   |     |

| PCI Master Function                                                                                                |     |

| PCI Slave Function                                                                                                 |     |

| BUFFER MANAGEMENT                                                                                                  |     |

| DESCRIPTORS INFORMATION                                                                                            |     |

| Transmit Descriptor Command Block Format                                                                           |     |

| Receive Descriptor Command Block Format                                                                            |     |

| FIFO AND CONTROL LOGIC                                                                                             |     |

| MEDIA TYPE AND AUTO-NEGOTIATION                                                                                    |     |

| AUTO-NEGOTIATED/FORCE MODE.                                                                                        |     |

| CAM BASED PERFECT FILTERING                                                                                        |     |

| Programming CAM                                                                                                    |     |

| Read CAM                                                                                                           |     |

| Unicast/Multicast Perfect Filtering.                                                                               |     |

| Interesting Packet Perfect Filtering                                                                               |     |

|                                                                                                                    |     |

| CHECKSUM OFFLOAD                                                                                                   |     |

| IEEE 802.1Q COMPLIANT VLANS                        |  |

|----------------------------------------------------|--|

| VLAN                                               |  |

| IEEE 802.1q VLANs<br>IEEE 802.1p Priority Transmit |  |

|                                                    |  |

| FLOW CONTROL                                       |  |

| STATISTICS<br>MIB Read Access                      |  |

| EEPROM INTERFACE                                   |  |

| EEPROM Direct Programming                          |  |

| EEPROM Embedded Programming                        |  |

| EEPROM Contents                                    |  |

| POWER MANAGEMENT<br>Wake On LAN                    |  |

| Wake On LAN<br>Wake Up Events                      |  |

| Power States                                       |  |

| РНҮ                                                |  |

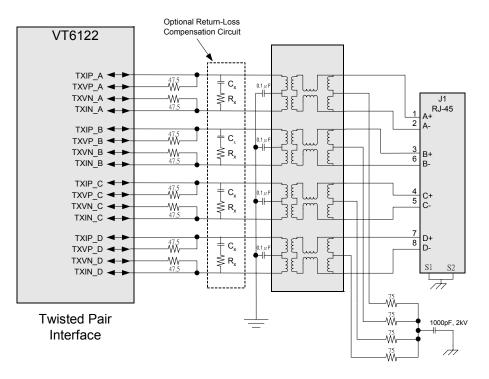

| TWISTED PAIR INTERFACE (TPI)                       |  |

| OPERATION MODE PRESETTING                          |  |

| System Clock Interface                             |  |

| TEST MODE INTERFACE (TMI)                          |  |

| Analog Front End (AFE)                             |  |

| DSP DATA PUMP CORE (PMA)                           |  |

| PHYSICAL CODING SUBLAYER (PCS)                     |  |

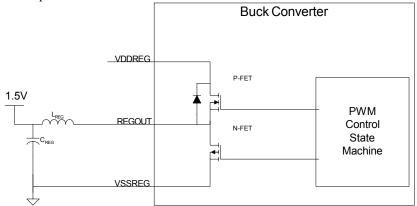

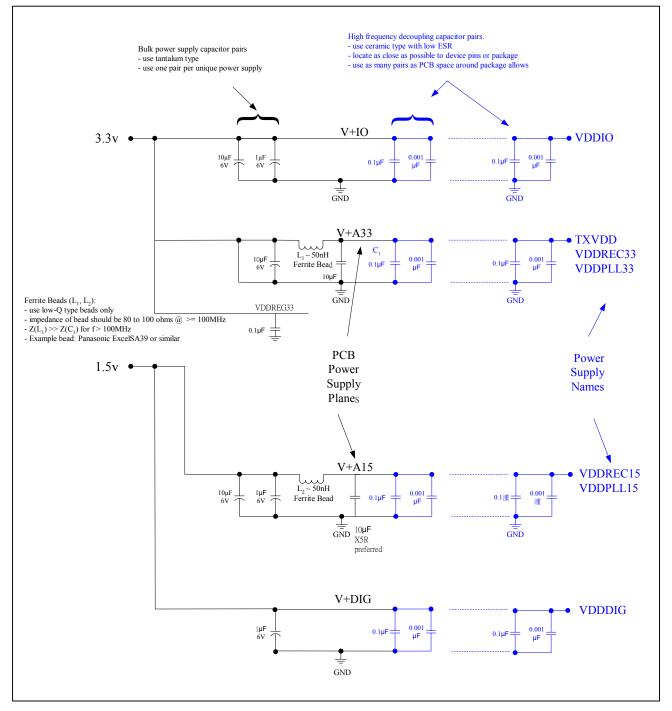

| OPTIONAL FIXED POWER SUPPLY REGULATOR              |  |

| PARALLEL LED INTERFACE                             |  |

| LED Control Spec                                   |  |

| TEST MODE INTERFACE (JTAG)                         |  |

| SUPPORTED INSTRUCTIONS AND INSTRUCTION CODES       |  |

| BOUNDARY-SCAN REGISTER CELL ORDER                  |  |

| AUTO-NEGOTIATION                                   |  |

| AUTO MDI / MDI-X FUNCTION                          |  |

| ACTIPHY <sup>™</sup> Power Management              |  |

| LECTRICAL SPECIFICATIONS                           |  |

| Absolute Maximum Ratings                           |  |

| DC SPECIFICATIONS                                  |  |

| TIMING SPECIFICATIONS                              |  |

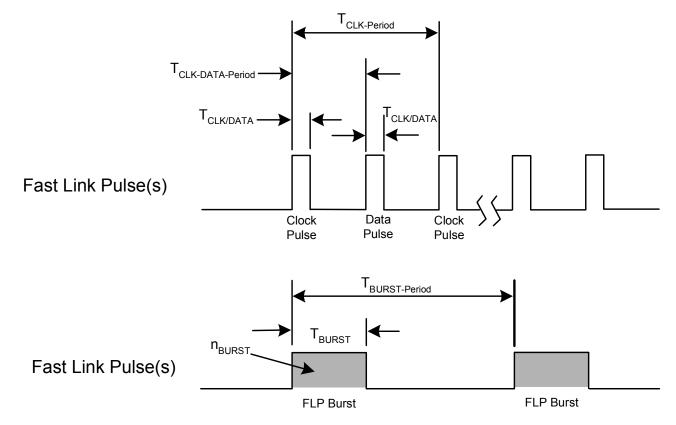

| Auto-Negotiation Fast Link Pulse (FLP) Timing      |  |

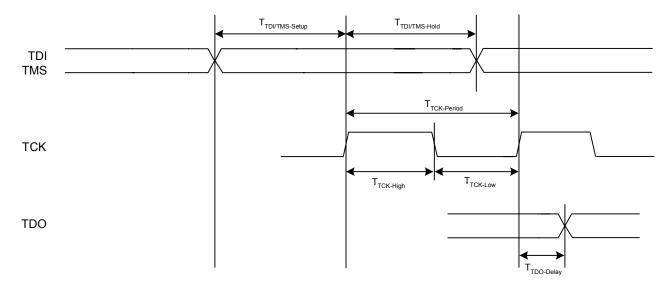

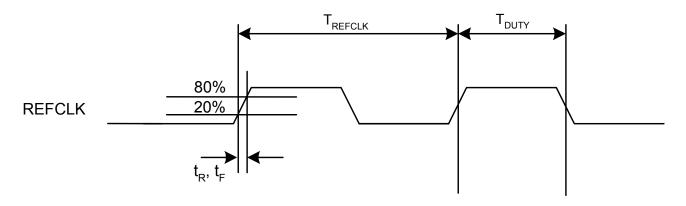

| JTAG Timing<br>X1/REFCLK Timing                    |  |

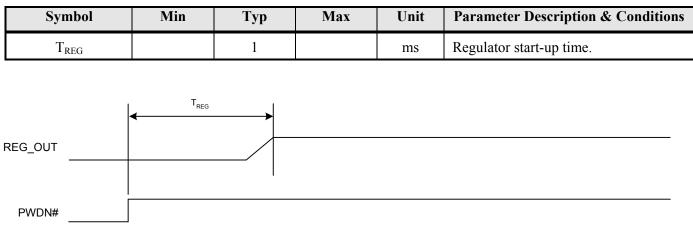

| Regulator Timing                                   |  |

| Oscillator Timing                                  |  |

| MAGNETICS SPECIFICATIONS                           |  |

| ECHANICAL SPECIFICATIONS                           |  |

#### List of Figures

| FIGURE 1. INTERNAL BLOCK DIAGRAM                             | . 3       |

|--------------------------------------------------------------|-----------|

| FIGURE 2. PIN DIAGRAM                                        | . 4       |

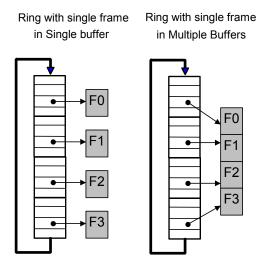

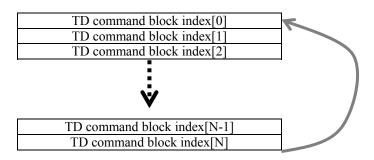

| FIGURE 3. BUFFER STRUCTURE                                   |           |

| FIGURE 4. BUCK CONVERTER ARCHITECTURAL SCHEMATIC             |           |

| FIGURE 5. 3.3V AND 1.5V POWER SUPPLY CONFIGURATION           | <b>D1</b> |

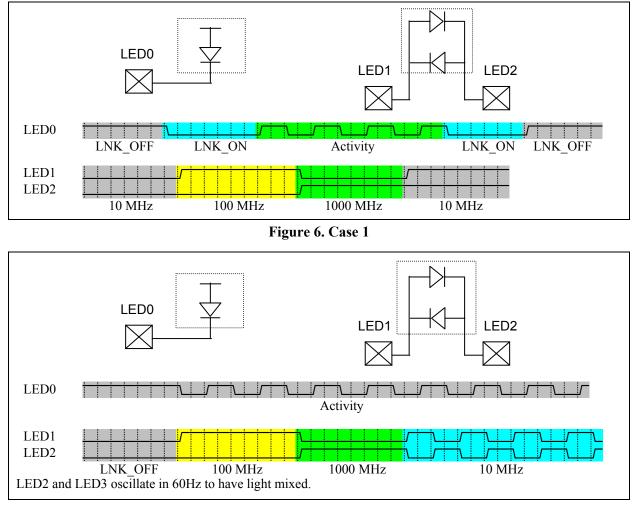

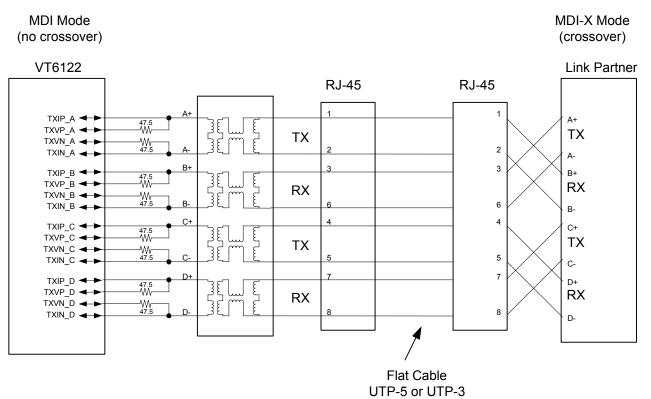

| FIGURE 6. CASE 1                                             |           |

| FIGURE 7. CASE 2                                             | )2        |

| FIGURE 8. CASE 3                                             |           |

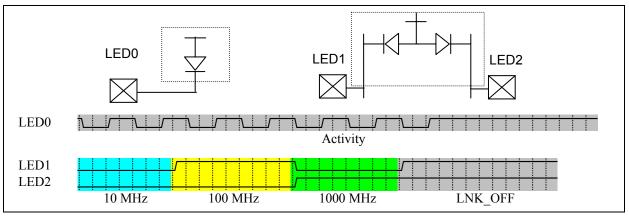

| FIGURE 9. TEST ACCESS PORT AND BOUNDARY SCAN ARCHITECTURE 10 | )4        |

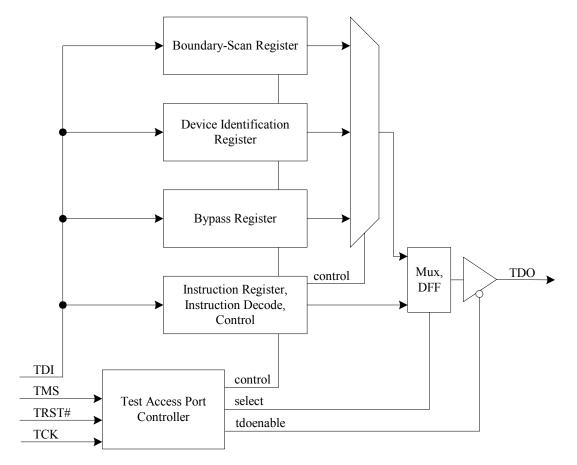

| FIGURE 10. MDI / MDI-X CROSSOVER EXAMPLE11                   | 14        |

| FIGURE 11. AUTO-NEGOTIATION FLP AC TIMING                    | 18        |

| FIGURE 12. JTAG INTERFACE AC TIMING                          | 19        |

| FIGURE 13. X1/REFCLK AC TIMING                               | 20        |

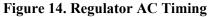

| FIGURE 14. REGULATOR AC TIMING                               | 21        |

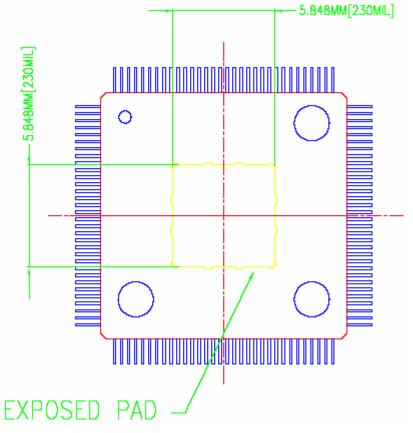

| FIGURE 15. OSCILLATOR AC TIMING                              | 21        |

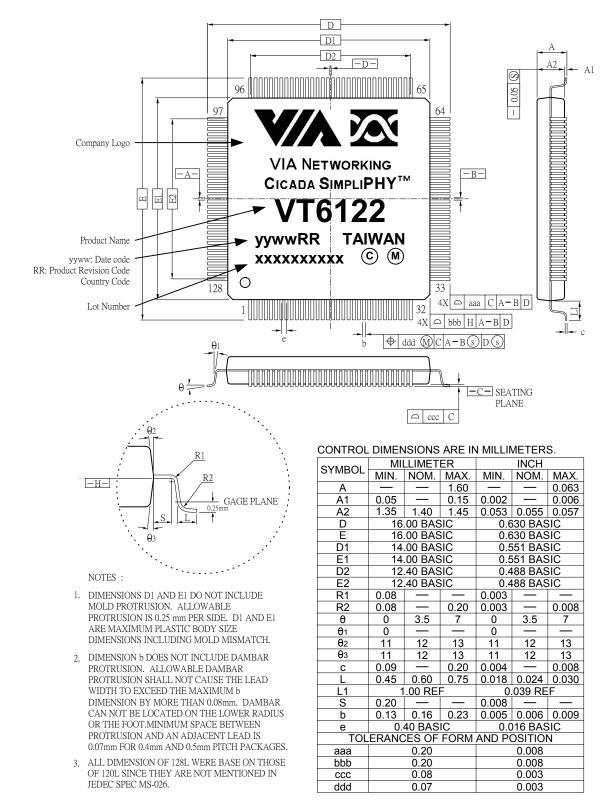

| FIGURE 16. 128-PIN EP-LOFP PACKAGE                           | 23        |

| FIGURE 17. BOTTOM VIEW OF 128-PIN EP-LQFP                    | 24        |

#### List of Tables

| TABLE 1. PIN LIST                                                      | 5   |

|------------------------------------------------------------------------|-----|

| TABLE 2. SIGNAL TYPE DEFINITIONS                                       | 5   |

| TABLE 3. PIN DESCRIPTIONS                                              | 6   |

| TABLE 4. PCI CONFIGURATION REGISTER MAP                                | 11  |

| TABLE 5. MII REGISTERS NAMES & ADDRESSES                               | 15  |

| TABLE 6. MII REGISTER RESET STICKY BITS                                |     |

| TABLE 7. 1000BASE-T TRANSMITTER/RECEIVER TEST MODES                    | 63  |

| TABLE 8. 1000BASE-T TRANSMITTER/RECEIVER TEST MODE 4 – QUINARY SYMBOLS | 63  |

| TABLE 9. 10BASE-T CURRENT REFERENCE TRIM VALUES                        |     |

| TABLE 10. CRS BEHAVIOR SELECTED BY OFFSET 16H BIT[2:1]                 |     |

| TABLE 11. 100/1000BASE-T TRANSMIT VOLTAGE REFERENCE TRIM VALUES        |     |

| TABLE 12. TX DESCRIPTOR COMMAND BLOCK STRUCTURE                        |     |

| TABLE 13. RECEIVE DESCRIPTOR FORMWT (RD)                               | 87  |

| TABLE 14. CHIP CONFIGURATION EEPROM CONTENTS                           |     |

| TABLE 15. POWER STATES                                                 |     |

| TABLE 16. LED SELECT                                                   |     |

| TABLE 17. PLI BIT DEFINITIONS                                          |     |

| TABLE 18. JTAG DEVICE IDENTIFICATION REGISTER DESCRIPTION              | 105 |

| TABLE 19. JTAG INTERFACE INSTRUCTION CODES                             | 106 |

| TABLE 20. VT6122 PORT ORDERING FROM TDI TO TDO                         | 108 |

| TABLE 21. ACCEPTED MDI PAIR CONNECTION COMBINATIONS                    | 113 |

| TABLE 22. ABSOLUTE MAXIMUM RATINGS                                     | 116 |

| TABLE 23. DC SPECIFICATIONS                                            | 117 |

| TABLE 24. CURRENT CONSUMPTION                                          |     |

| TABLE 25. AUTO-NEGOTIATION FLP AC TIMING SPECIFICATION                 |     |

| TABLE 26. JTAG INTERFACE AC TIMING SPECIFICATION                       |     |

| TABLE 27. REFCLK AC TIMING SPECIFICATIONS                              |     |

| TABLE 28. REGULATOR AC TIMING SPECIFICATIONS                           | 121 |

## VT6122 Gigabit Ethernet Controller

## **PRODUCT FEATURES**

#### • Feature

- Fully IEEE 802.3 2002 compliant

- Optional on-chip switching regulator circuit

- Automatic detection and correction of cable pair swaps, pair skew, and pair polarity, along with an automatic MDI/MDI-X crossover function

- Optional integrated oscillator circuit

- Five direct-drive LED pins with four programmable LED modes

- Low EMI line drivers with robust CESD performance

- Manufactured in mainstream 3.3V/1.5V digital CMOS process

#### • Bus Architecture.

- Compliance to PCI Rev. 2.2, 33/66 MHz, 32 bit

- PCI Bus master Dual Channel DMA support for Tx/Rx

- Tx/Rx descriptor Scatter and Gather support in host memory

- No Transmit data byte alignment restriction; Rx data buffer should be double-word aligned

- Flexible programmable Bus master burst sizes and advanced internal arbitration control to optimize the bus utilization

- 256 bytes IO map/ 256 bytes memory map IO range in 32-bit addressing

- 64-bit addressing option in EEPROM

- Bus Master 64-bit addressing

- Use global Descriptor DMA and FIFO DMA Hi-16 bit address

- Adaptive interrupt service scheme for interrupt coalescence

#### • Network Functionality

- 64 x 48 CAM for 32 perfect filtering and 32 interest packet-perfect filtering

- 16 kilobyte jumbo frame support

- Integrated 16 kilobyte ( $2048 \times 64$ ) TX FIFO, 48 kilobytes ( $6144 \times 64$ ) RXFIFO for high performance applications

#### Network Management

- WFM 2.0 enabled for server

- SNMP management, DMI 2.0, PXE 2.1

- ACPI, Wake On LAN, and Microsoft onNow

- PCI PMU 1.1

- 802.1Q VLAN,  $64 \times 12$  CAM VLAN ID perfect filtering

- Long frame support (1518 + 4)

- VLAN tag insertion for transmit packets

- VLAN tag detection and removal for receive packets

- 802.1p four-level priority transmit. (MAC support 4 TD, 1 RD queue)

- Checksum offload

- IPv4 checksum task offload

- IEEE 802.1Q compliant VLAN are supported

- Fragmented IP datagrams are not supported

- Tx checksum generation for IP (IP option), TCP, and UDP

- Rx checksum validation for IP (IP option), TCP, and UDP

- Statistics for RFC 1213 (MIB II) RFC 1398 (etherLike MIB) 802.3 LME

- Large Packet Segmentation Offload

#### • Miscellaneous Supports

- 16-word 93c46/93c06 serial ROM interface, support

- Embedded random word access

- Dynamic and power-up loading to update chip default configuration

- Software-driven direct programming

- Supports Shadow-EEPROM function to work without an external EEPROM device

Built-in 16-word shadow memory to store EEPROM data

- Supports four modes of LED behaviors. (five LED pins)

- Build-in power-switching regulator to simplify power partition on board

#### Advanced Software Support

- GigaCheck: NIC management application in Windows platform.

- DMI-GE: DMI CI and MA in Windows platform

- VSNMP-GE: SNMP extension agent in Windows platform

- VeriPHY<sup>™</sup> Link Management Suite: integrated into GigaCheck cable analysis and link analysis function

#### • Technology

- 1.5V core power and 3.3V I/O power with 5V PCI tolerant inputs

- 14 mm × 14 mm, 128-pin LQFP with 0.4 mm pin pitch

#### • System Application

- Desktop NIC

- LAN-on-Motherboard and Mobile PC NICs

## **OVERVIEW**

VT6122 is a PCI Rev. 2.2 10/100/1000 MHz integrated single chip (MAC + PHY) for Network Interface Card (NIC) and LAN On Motherboard (LOM) applications. It is a high-performance network solution for workstations and servers, offering two gigabits per second of aggregated bandwidth. Support for the VT6122 includes critical performance and management related advanced features.

The VT6122 is fully compliant with PCI power management Rev. 1.1 and ACPI Rev. 1.0. It implements multiple wake-up events including magic packets, pattern-match packets, and link-status changes. The VT6122 also support AC power loss and PCI abnormal shut down wake up cases on Magic packet power management mechanisms.

The driver and silicon have been developed together to provide the optimal performance in term of both throughput and host CPU utilization.

The twisted pair interface includes an innovative internal hybrid and a very low EMI line driver with robust Cable Sourced ESD (CESD) performance, allowing the use of the lowest-cost 1:1 magnetic modules, minimum external components, and less complex PCB traces. To further reduce system complexity and cost, the VT6122 can optionally be powered from a single 3.3V power supply when utilizing the device's on-chip regulator control circuit to produce the 1.5V core power supply voltage.

The VT6122 leverages Cicada's proprietary MicroPHY<sup>™</sup> DSP Technology, key to enabling an extremely low-power Gigabit PHY on a single chip. Cicada's mixed signal and DSP architecture yields robust performance, supporting both full- and half-duplex 10BASE-T, 100BASE-TX, and 1000BASE-T Ethernet over unshielded twisted pair (UTP) cable, with more than 5 dB of design margin with respect to all worst- case impairments (NEXT, FEXT, Echo, and system noise). The industry's highest-performance, lowest-power DSP-based transceiver utilizes an optimum trellis decoding algorithm in concert with all digital gain control and timing recovery.

To enable maximum network management feedback to the host system and the user, VeriPHY<sup>™</sup> Link Management Suite routines allow extensive network and cable plant operating and status information, such as the cable length and effective Bit Error Rate (BER) that greatly simplifies Gigabit Ethernet network deployment and management.

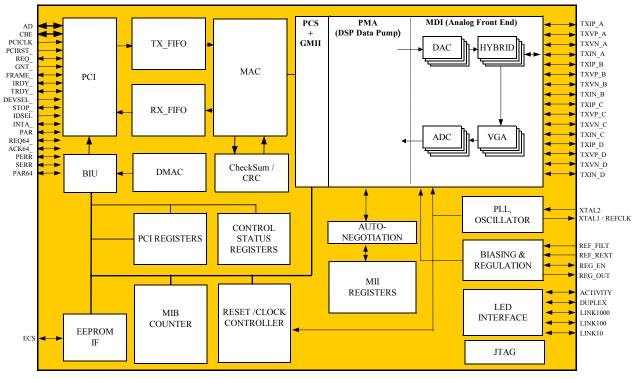

Figure 1. Internal Block Diagram

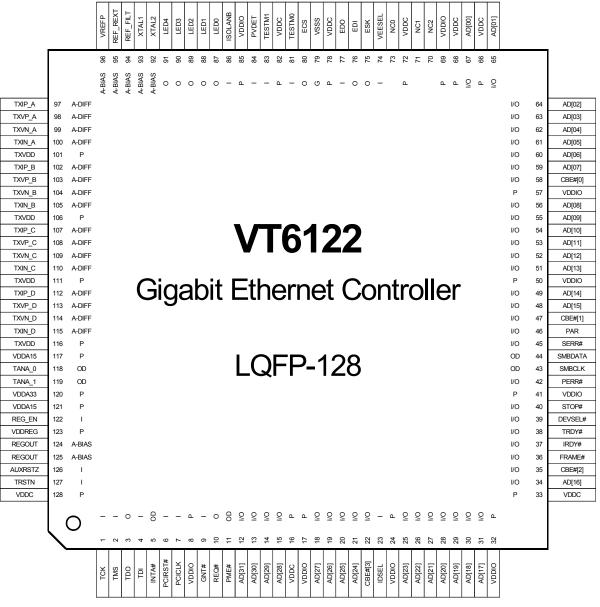

PINOUT

Figure 2. Pin Diagram

| Name   | No. | Туре |

|--------|-----|------|

| AD[00] | 67  | I/O  |

| AD[01] | 65  | I/O  |

| AD[02] | 64  | I/O  |

| AD[03] | 63  | I/O  |

| AD[04] | 62  | I/O  |

| AD[05] | 61  | I/O  |

| AD[06] | 60  | I/O  |

| AD[07] | 59  | I/O  |

| AD[08] | 56  | I/O  |

| AD[09] | 55  | I/O  |

| AD[10] | 54  | I/O  |

| AD[11] | 53  | I/O  |

| AD[12] | 52  | I/O  |

| AD[13] | 51  | I/O  |

| AD[14] | 49  | I/O  |

| AD[15] | 48  | I/O  |

| AD[16] | 34  | I/O  |

| AD[17] | 31  | I/O  |

| AD[18] | 30  | I/O  |

| AD[19] | 29  | I/O  |

| AD[20] | 28  | I/O  |

| AD[21] | 27  | I/O  |

| AD[22] | 26  | I/O  |

| AD[23] | 25  | I/O  |

| AD[24] | 21  | I/O  |

| AD[25] | 20  | I/O  |

| AD[26] | 19  | I/O  |

| AD[27] | 18  | I/O  |

| AD[28] | 15  | I/O  |

| AD[29] | 14  | I/O  |

| AD[30] | 13  | I/O  |

| AD[31] | 12  | I/O  |

Table 1. Pin List

| Name               | No. | Туре   |

|--------------------|-----|--------|

| AUXRSTZ            | 126 | I      |

| CBE#[0]            | 58  | I/O    |

| CBE#[1]            | 47  | I/O    |

| CBE#[2]            | 35  | I/O    |

| CBE#[3]<br>DEVSEL# | 22  | I/O    |

| DEVSEL#            | 39  | I/O    |

| ECS                | 80  | 0      |

| EDI<br>EDO         | 76  | 0      |

|                    | 77  |        |

| ESK                | 75  | 0      |

| FRAME#             | 36  | I/O    |

| GNT#               | 9   |        |

| IDSEL              | 23  |        |

| INTA#              | 5   | OD     |

| IRDY#              | 37  | I/O    |

| ISOLANB            | 86  |        |

| LED0               | 87  | 0      |

| LED1               | 88  | 0      |

| LED2               | 89  | 0      |

| LED3               | 90  | 0      |

| LED4               | 91  | 0      |

| NC0                | 73  |        |

| NC1                | 71  |        |

| NC2                | 70  |        |

| PAR                | 46  | I/O    |

| PCICLK             | 7   | I      |

| PCIRST#            | 6   | I      |

| PERR#              | 42  | I/O    |

| PME#               | 11  | OD     |

| PVDET              | 84  |        |

| REF_FILT           | 94  | A-BIAS |

| REF_REXT           | 95  | A-BIAS |

| Name    | No. | Туре   |

|---------|-----|--------|

| REG_EN  | 122 | I      |

| REGOUT  | 124 | A-BIAS |

| REGOUT  | 125 | A-BIAS |

| REQ#    | 10  | 0      |

| SERR#   | 45  | I/O    |

| SMBCLK  | 43  | OD     |

| SMBDATA | 44  | OD     |

| STOP#   | 40  | I/O    |

| TANA_0  | 118 | OD     |

| TANA_1  | 119 | OD     |

| ТСК     | 1   |        |

| TDI     | 4   |        |

| TDO     | 3   | 0      |

| TESTM0  | 81  |        |

| TESTM1  | 83  |        |

| TMS     | 2   |        |

| TRDY#   | 38  | I/O    |

| TRSTN   | 127 |        |

| TXIN_A  | 100 | A-DIFF |

| TXIN_B  | 105 | A-DIFF |

| TXIN_C  | 110 | A-DIFF |

| TXIN_D  | 115 | A-DIFF |

| TXIP_A  | 97  | A-DIFF |

| TXIP_B  | 102 | A-DIFF |

| TXIP_C  | 107 | A-DIFF |

| TXIP_D  | 112 | A-DIFF |

| TXVDD   | 101 | Р      |

| TXVDD   | 106 | Р      |

| TXVDD   | 111 | Р      |

| TXVDD   | 116 | Р      |

| TXVN_A  | 99  | A-DIFF |

| TXVN_B  | 104 | A-DIFF |

| Name   | No. | Туре   |

|--------|-----|--------|

| TXVN_C | 109 | A-DIFF |

| TXVN_D | 114 | A-DIFF |

| TXVP_A | 98  | A-DIFF |

| TXVP_B | 103 | A-DIFF |

| TXVP_C | 108 | A-DIFF |

| TXVP_D | 113 | A-DIFF |

| VDDA15 | 117 | Р      |

| VDDA15 | 121 | Р      |

| VDDA33 | 120 | Р      |

| VDDC   | 16  | Р      |

| VDDC   | 33  | Р      |

| VDDC   | 66  | Р      |

| VDDC   | 68  | Р      |

| VDDC   | 72  | Р      |

| VDDC   | 78  | Р      |

| VDDC   | 82  | Р      |

| VDDC   | 128 | Р      |

| VDDIO  | 8   | Р      |

| VDDIO  | 17  | Р      |

| VDDIO  | 24  | Р      |

| VDDIO  | 32  | Р      |

| VDDIO  | 41  | Р      |

| VDDIO  | 50  | Р      |

| VDDIO  | 57  | Р      |

| VDDIO  | 69  | Р      |

| VDDIO  | 85  | Р      |

| VDDREG | 123 | Р      |

| VEESEL | 74  | I      |

| VREFP  | 96  | A-BIAS |

| VSSS   | 79  | G      |

| XTAL1  | 93  | A-BIAS |

| XTAL2  | 92  | A-BIAS |

#### Table 2. Signal Type Definitions

| Туре              | Description                                                                                                              |  |  |  |

|-------------------|--------------------------------------------------------------------------------------------------------------------------|--|--|--|

| Ι                 | Input. Input is a standard input-only signal.                                                                            |  |  |  |

| 0                 | Output. This is a standard active output driver.                                                                         |  |  |  |

| I/O               | Input/Output. This is an input/output signal                                                                             |  |  |  |

| T/S               | Tri-State. Tri-state is an inactive bi-directional input/output pin                                                      |  |  |  |

| OD                | <b>Open Drain</b> . It allows multiple devices to share as a wire-OR.                                                    |  |  |  |

| A <sub>DIFF</sub> | Analog differential signal pair for twisted pair interface.                                                              |  |  |  |

| A <sub>BIAS</sub> | Analog bias or reference signal. Must be tied to external resistor and/or capacitor bias network, as shown in the system |  |  |  |

|                   | schematic in Figure 2.                                                                                                   |  |  |  |

| Р                 | Power supply pin                                                                                                         |  |  |  |

| G                 | Ground pin                                                                                                               |  |  |  |

| PCI Bus Interface |                      |      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |  |  |

|-------------------|----------------------|------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| Name              | Number               | Туре | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                              |  |  |

| AD[31:0]          | See<br>Table 1       | I/O  | Address and Data. Multiplexed address and data bus. A bus transaction consists of an address phase followed by one or more data phases. The address phase is the clock cycle in which FRAME# is asserted. Write data is stable and valid when IRDY# is asserted and read data is stable and valid when TRDY# is asserted.                                                                                                                                                |  |  |

| PCIRST#           | 6                    | I    | <b>PCI Reset.</b> When PCIRST# is asserted low, the chip performs an internal system hardware reset. PCIRST# may be asynchronous to PCICLK when asserted or de-asserted. It is recommended that the deassertion be synchronous to guarantee clean and bounce-free edge.                                                                                                                                                                                                  |  |  |

| PCICLK            | 7                    | Ι    | <b>PCI Clock</b> . Provides timing for all transactions on PCI and is an input pin to every PCI device. The clock frequency range is from 0 to 66 MHz.                                                                                                                                                                                                                                                                                                                   |  |  |

| GNT#              | 9                    | Ι    | Bus grant: Asserts to indicate to the device that access to the bus is granted.                                                                                                                                                                                                                                                                                                                                                                                          |  |  |

| IDSEL             | 23                   | Ι    | <b>ID Select.</b> Used as a chip select during PCI configuration cycle.                                                                                                                                                                                                                                                                                                                                                                                                  |  |  |

| INTA#             | 5                    | OD   | <b>Interrupt</b> is an asynchronous signal which is used to request an interrupt                                                                                                                                                                                                                                                                                                                                                                                         |  |  |

| REQ#              | 10                   | 0    | <b>Bus request</b> is asserted by the bus master indicate to the bus arbiter that it wants to use the bus.                                                                                                                                                                                                                                                                                                                                                               |  |  |

| CBE#[3:0]         | 22<br>35<br>47<br>58 | I/O  | <b>Bus Command/Byte Enables:</b> are multiplexed on the same PCI pins. During the address phase of a transaction, CBE[3:0]# define the Bus Command. During the data phase, CBE[3:0]# are used as Byte Enables. The Byte Enables define which physical byte lanes carry meaningful data. CBE0# applies to byte 0 and CBE3# applies to byte 3.                                                                                                                             |  |  |

| PAR               | 46                   | I/O  | <b>Parity</b> is even parity across AD31-0 and CBE3-0#. PAR is stable and valid one clock after the address phase. For data phases PAR is stable and valid one clock after either IRDY# is asserted on a write transaction or TRDY# is asserted on a read transaction.                                                                                                                                                                                                   |  |  |

| FRAME#            | 36                   | I/O  | <b>Frame</b> : Frame is driven by the current master to indicate the beginning and duration of an access. FRAME# is asserted to indicate a bus transaction is beginning. While FRAME# is asserted, data transfers continue. When FRAME# is de-asserted, the transaction is in the final data phase.                                                                                                                                                                      |  |  |

| IRDY#             | 37                   | I/O  | <b>Initiator Ready</b> indicates the initiating agent's ability to complete the current data phase of the transaction. IRDY# is used in conjunction with TRDY#. A data phase is completed on any clock when both IRDY# and TRDY# are asserted. During a write, IRDY# indicates that valid data is present on AD31-0. During a read, it indicates the master is prepared to accept data. Wait cycles are inserted until both IRDY# and TRDY# are asserted simultaneously. |  |  |

| TRDY#             | 38                   | I/O  | <b>Target Ready</b> indicates the target's agent's ability to complete the current data phase of the transaction. TRDY# is used in conjunction with IRDY#. A data phase is completed on any clock when both IRDY# and TRDY# are asserted. During a read, TRDY# indicates that valid data is present on AD31-0. During a write, it indicates the target is prepared to accept data. Wait cycles are inserted until both IRDY# and TRDY# are asserted simultaneously.      |  |  |

| DEVSEL#           | 39                   | I/O  | <b>Device Select</b> . When actively driven, indicates the driving device has decoded its address as the target of the current access. As an input, DEVSEL# indicates whether any device on the bus has been selected.                                                                                                                                                                                                                                                   |  |  |

| STOP#             | 40                   | I/O  | Stop. The device drives STOP# to disconnect further transactions.                                                                                                                                                                                                                                                                                                                                                                                                        |  |  |

| PERR#             | 42                   | I/O  | <b>Parity error</b> . VT6122 as a master or target will assert this signal low when a data parity error is detected on any incoming data. As a master, it will monitor this signal on all write transactions.                                                                                                                                                                                                                                                            |  |  |

| SERR#             | 45                   | I/O  | <b>System Error</b> . This signal is asserted low by VT6122 during address parity error and system errors if enabled.                                                                                                                                                                                                                                                                                                                                                    |  |  |

| SMBCLK            | 43                   | OD   | SMBus interface Clock signal. Not available in VT6122.                                                                                                                                                                                                                                                                                                                                                                                                                   |  |  |

| SMBDATA           | 44                   | OD   | SMBus interface Data signal. Not available in VT6122.                                                                                                                                                                                                                                                                                                                                                                                                                    |  |  |

V

| Power Management Interface |                              |    |                                                                                |  |  |

|----------------------------|------------------------------|----|--------------------------------------------------------------------------------|--|--|

| Name                       | Name Number Type Description |    |                                                                                |  |  |

| PME#                       | 11                           | OD | <b>Power management event.</b> This signal is asserted low to indicate a power |  |  |

|                            |                              |    | management event has occurred.                                                 |  |  |

| Local Memory Interface |                              |   |                                                                               |  |

|------------------------|------------------------------|---|-------------------------------------------------------------------------------|--|

| Name                   | Name Number Type Description |   |                                                                               |  |

| VEESEL                 | 74                           | Ι | Virtual EEPROM Enable: To enable the Virtual EEPROM function, this pin should |  |

|                        |                              |   | be tied to LOW.                                                               |  |

| ESK                    | 75                           | 0 | EEPROM Clock: External serial EEPROM clock                                    |  |

| EDI                    | 76                           | 0 | <b>EEPROM Data In:</b> External serial EEPROM data input.                     |  |

| EDO                    | 77                           | Ι | EEPROM Data Out: External serial EEPROM data output.                          |  |

| ECS                    | 80                           | 0 | EEPROM Chip Select. Chip select signal of the external EEPROM                 |  |

| Miscellaneous Interface |                             |   |                                                                                                     |  |  |

|-------------------------|-----------------------------|---|-----------------------------------------------------------------------------------------------------|--|--|

| Name                    | ame Number Type Description |   |                                                                                                     |  |  |

| TESTM0                  | 81                          | Ι | Operation mode setting 0                                                                            |  |  |

| TESTM1                  | 83                          | Ι | Operation mode setting 1                                                                            |  |  |

| AUXRSTZ                 | 126                         | Ι | External RC for suspend power on reset for testing purpose                                          |  |  |

| PVDET                   | 84                          | Ι | Schmitt-trigger tied down input, used for global single power design approach to monitor PCI power. |  |  |

| ISOLAN#                 | 86                          | Ι | Isolate LAN chip, active low.                                                                       |  |  |

| Media Interface Signals |        |                   |                                                                                                                                                                                                                                                 |  |  |  |  |

|-------------------------|--------|-------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| Name                    | Number | Туре              | Description                                                                                                                                                                                                                                     |  |  |  |  |

| TXIP_A                  | 97     | A <sub>DIFF</sub> | <b>TX/RX Channel "A" positive hybrid pair.</b><br>Positive differential pair connected to external termination resistors and then to the                                                                                                        |  |  |  |  |

| TXVP_A                  | 98     | A <sub>DIFF</sub> | positive primary side of the transformer. This pin pair forms the positive signal of the "A" data channel. In all three speeds, these pins generate the secondary side signal, normally connected to RJ-45 pin 1.                               |  |  |  |  |

| TXIN_A                  | 100    | A <sub>DIFF</sub> | <b>TX/RX Channel "A" negative hybrid pair.</b><br>Negative differential pair connected to external termination resistors and then to the negative primary side of the transformer. This pin pair forms the negative signal of                   |  |  |  |  |

| TXVN_A                  | 99     | A <sub>DIFF</sub> | the "A" data channel. In all three speeds, these pins generate the secondary side signal, normally connected to RJ-45 pin 2.                                                                                                                    |  |  |  |  |

| TXIP_B                  | 102    | A <sub>DIFF</sub> | <b>TX/RX Channel "B" positive hybrid pair.</b><br>Positive differential pair connected to external termination resistors and then to the positive primary side of the transformer. This pin pair forms the positive signal of the               |  |  |  |  |

| TXVP_B                  | 103    | A <sub>DIFF</sub> | "B" data channel. In all three speeds, these pins generate the secondary side signal,<br>normally connected to RJ-45 pin 3.                                                                                                                     |  |  |  |  |

| TXIN_B                  | 105    | A <sub>DIFF</sub> | <b>TX/RX Channel "B" negative hybrid pair.</b><br>Negative differential pair connected to external termination resistors and then to the negative primary side of the transformer. This pin pair forms the negative signal of                   |  |  |  |  |

| TXVN_B                  | 104    | A <sub>DIFF</sub> | negative primary side of the transformer. This pin pair forms the negative signal of the "B" data channel. In all three speeds, these pins generate the secondary side signal, normally connected to RJ-45 pin 6.                               |  |  |  |  |

| TXIP_C                  | 107    | A <sub>DIFF</sub> | <b>TX/RX Channel "C" positive hybrid pair.</b><br>Positive differential pair connected to external termination resistors and then to the positive primary side of the transformer. This pin pair forms the positive signal of the               |  |  |  |  |

| TXVP_C                  | 108    | A <sub>DIFF</sub> | "C" data channel. In 1000 Mb mode, these pins generate the secondary side signal,<br>normally connected to RJ-45 pin 4 (pins not used in 10M/100M modes).                                                                                       |  |  |  |  |

| TXIN_C                  | 110    | A <sub>DIFF</sub> | <b>TX/RX Channel "C" negative hybrid pair.</b><br>Negative differential pair connected to external termination resistors and then to the negative primary side of the transformer. This pin pair forms the negative signal of                   |  |  |  |  |

| TXVN_C                  | 109    | A <sub>DIFF</sub> | negative primary side of the transformer. This pin pair forms the negative signal of the "C" data channel. In 1000 Mb mode, these pins generate the secondary side signal, normally connected to RJ-45 pin 5 (pins not used in 10M/100M modes). |  |  |  |  |

| TXIP_D                  | 112    | A <sub>DIFF</sub> | <b>TX/RX Channel "D" positive hybrid pair.</b><br>Positive differential pair connected to external termination resistors and then to the positive primary side of the transformer. This pin pair forms the positive signal of the               |  |  |  |  |

| TXVP_D                  | 113    | A <sub>DIFF</sub> | "D" data channel. In 1000 Mb mode, these pins generate the secondary side signal, normally connected to RJ-45 pin 7 (pins not used in 10M/100M modes).                                                                                          |  |  |  |  |

| TXIN_D                  | 115    | A <sub>DIFF</sub> | <b>TX/RX Channel "D" negative hybrid pair.</b><br>Negative differential pair connected to external termination resistors and then to the negative primary side of the transformer. This pin pair forms the negative signal of                   |  |  |  |  |

| TXVN_D                  | 114    | A <sub>DIFF</sub> | the "D" data channel. In 1000 Mb mode, these pins generate the secondary side signal, normally connected to RJ-45 pin 8 (pins not used in 10M/100M modes).                                                                                      |  |  |  |  |

6

| JTAG Interface |        |      |                                                                                        |  |  |  |

|----------------|--------|------|----------------------------------------------------------------------------------------|--|--|--|

| Name           | Number | Туре | Description                                                                            |  |  |  |

| TDI            | 4      | Ι    | JTAG Test Data Serial Input. Serial test pattern data is scanned into the device on    |  |  |  |

|                |        |      | this input pin, which is sampled with respect to the rising edge of TCK. This pin      |  |  |  |

|                |        |      | should be tied high during normal chip operation.                                      |  |  |  |

| TDO            | 3      | 0    | JTAG Test Data Serial Output. Serial test data is driven out of the device on the      |  |  |  |

|                |        |      | falling edge of TCK. This pin should be left floating during normal chip operation.    |  |  |  |

| TMS            | 2      | Ι    | JTAG Test Mode Select. This input pin, sampled on the rising edge of TCK,              |  |  |  |

|                |        |      | controls the TAP (Test Access Port) controller's 16-state instruction state machine.   |  |  |  |

|                |        |      | This pin should be tied high during normal chip operation                              |  |  |  |

| TCK            | 1      | Ι    | JTAG Test Clock. This input pin is the master clock source used to control all JTAG    |  |  |  |

|                |        |      | test logic in the device. This pin should be tied low during normal chip operation.    |  |  |  |

| TRST#          | 127    | Ι    | JTAG Reset. This active low input pin serves as an asynchronous reset to the JTAG      |  |  |  |

|                |        |      | TAP controller's state machine. As required by the JTAG standard, this pin includes    |  |  |  |

|                |        |      | an on-chip pull-up resistor. Alternatively, if the JTAG port of the device is not used |  |  |  |

|                |        |      | on the printed circuit board, then this pin should be tied to ground (VSSIO) with a    |  |  |  |

|                |        |      | pull-down resistor.                                                                    |  |  |  |

| LED Status Output |                              |   |                                                                                                                                                                                                       |  |  |  |

|-------------------|------------------------------|---|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| Name              | Name Number Type Description |   |                                                                                                                                                                                                       |  |  |  |

| LED[4:0]          | 87, 88, 89<br>90, 91         | Ö | <b>LED Status Outputs.</b> Output pins for directly driving status LEDs.<br>When enabled by MII register bit 27.3, all LED outputs are pulsed at 5 kHz with a 20% duty cycle for low-power operation. |  |  |  |

|                  | System Clock Interface |      |                                                                                                                                                                                                                                                                                                            |  |  |  |

|------------------|------------------------|------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| Name             | Number                 | Туре | Description                                                                                                                                                                                                                                                                                                |  |  |  |

| XTAL1/<br>REFCLK | 93                     | Ι    | <b>Crystal Input</b> / <b>Reference Clock Input.</b> The reference input clock can be 25 MHz, with a +50 ppm frequency tolerance or connected to a 25 MHz, parallel resonant crystal with a +50 ppm frequency tolerance. When used with a crystal, a 33 pF capacitor is connected from this pin to ground. |  |  |  |

| XTAL2            | 92                     | Ō    | <b>Crystal Output.</b> 25 MHz parallel resonant crystal output. If the on-chip oscillator is enabled, a 33 pF capacitor is connected from this output to ground.                                                                                                                                           |  |  |  |

|          | Regulator Control and Analog Bias Pins |                   |                                                                                                                                                                                                                                                                      |  |  |  |

|----------|----------------------------------------|-------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| Name     | Number                                 | Туре              | Description                                                                                                                                                                                                                                                          |  |  |  |

| REF_REXT | 95                                     | A <sub>BIAS</sub> | Bias pin to external 2.26k (1%) resistor tied to analog ground                                                                                                                                                                                                       |  |  |  |

| REF_FILT | 94                                     | A <sub>BIAS</sub> | <b>Reference Generator Filter</b> pin to external 1 µF (+/-10%) capacitor tied to analog ground.                                                                                                                                                                     |  |  |  |

| VREFP    | 96                                     | A <sub>BIAS</sub> | <b>Positive Reference Bias.</b> Analog reference generator positive supply input. VREFP should be tied to analog 3.3V supply with a short signal trace. A 1 $\mu$ F capacitor should be placed between VREFP and ground, as close to the device package as possible. |  |  |  |

| REG_EN   | 122                                    | Ι                 | <b>Regulator Control Enable.</b> Active High input enables on-chip switching regulator in order to generate the 1.5V supply voltage. Includes on-chip 100 k $\Omega$ pull-up resistor to VDD                                                                         |  |  |  |

| TANA_0   | 118                                    | N/C               | Test Pin. These pins are open drain, which are used for debugging only and should                                                                                                                                                                                    |  |  |  |

| TANA_1   | 119                                    | N/C               | be no-connects in a custom design.                                                                                                                                                                                                                                   |  |  |  |

| REGOUT   | 124, 125                               | A <sub>BIAS</sub> | <b>Regulator output.</b> Used to drive an external inductor and capacitor.                                                                                                                                                                                           |  |  |  |

| VDDREG   | 123                                    | Р                 | Switching regulator 3.3V supply                                                                                                                                                                                                                                      |  |  |  |

| Analog Power Supply Signal Description |                              |   |                                |  |  |

|----------------------------------------|------------------------------|---|--------------------------------|--|--|

| Name                                   | Name Number Type Description |   |                                |  |  |

| TXVDD                                  | 101, 106                     | Р | Line driver supply (3.3V)      |  |  |

|                                        | 111, 116                     |   |                                |  |  |

| VDDA15                                 | 121, 117                     | Р | Power. Analog 1.5V core power. |  |  |

| VDDA33                                 | 120                          | Р | Power. Analog 3.3V core power. |  |  |

|         | Digital Power Supply Signal Description |   |                          |  |  |  |  |

|---------|-----------------------------------------|---|--------------------------|--|--|--|--|

| Name    | Name Number Type Description            |   |                          |  |  |  |  |

| VDDIO   | See Table 1                             | Р | I/O power supply (3.3V)  |  |  |  |  |

| VDDC    | See Table 1                             | Р | Core power supply (1.5V) |  |  |  |  |

| VSSS    | 79                                      | G | Core ground (0V)         |  |  |  |  |

| NC[2:0] | 70, 71, 73                              |   | No connect               |  |  |  |  |

### REGISTERS

#### **Register Map Tables**

#### **PCI Configuration Space**

| Byte 3                   | Byte 2              | Byte 1          |                  | Byte 0                                                | Offset (Hex) |  |  |  |

|--------------------------|---------------------|-----------------|------------------|-------------------------------------------------------|--------------|--|--|--|

| Device II                |                     |                 | Vendor ID (1106) |                                                       |              |  |  |  |

| STATUS                   |                     |                 | COMMANE          |                                                       | 00 04        |  |  |  |

|                          | ASS CODE (02 00 00) |                 |                  | ev ID (10)                                            | 04           |  |  |  |

|                          |                     | LAT Timer       |                  |                                                       |              |  |  |  |

| <b>BIST</b> (00)         | Header type         |                 |                  | Cache Line                                            | 0C           |  |  |  |

| (00)                     | (00)                | (R/W)           |                  | (R/W)                                                 | 10           |  |  |  |

| CSR IO Mapped Base Add   |                     |                 | 0                | $\begin{array}{c ccccccccccccccccccccccccccccccccccc$ | 10           |  |  |  |

| CSR MEM Mapped Base A    | .ddr (256 Bt) 000   |                 | 0                | 0 0 0 0                                               | 14           |  |  |  |

| 32'h0000_0000            |                     |                 |                  |                                                       | 20           |  |  |  |

| SUB System ID            | 17                  | SUB Vendor ID   | 000000000        | 000 F                                                 | 2C           |  |  |  |

| Expansion Rom Base Addre |                     | 15 14 13        | 00000000         |                                                       | 30           |  |  |  |

|                          | 24'h0               |                 | C.               | APABILITY<br>(50)h                                    | 34           |  |  |  |

| Max_LAT                  | Min_GNT             | INT PIN<br>(01) | 4'h0             | INTLN<br>[3:0]                                        | 3C           |  |  |  |

|                          | 40-4F               |                 |                  |                                                       |              |  |  |  |

|                          | Р                   | MU CAPABILITIE  | S                |                                                       |              |  |  |  |

| PMC(                     |                     | NIPTR(00)       | -                | 01                                                    | 50 h         |  |  |  |

| DATA(00)                 | BSE(00)h            | S 0000000       | E 0000           | 00 WS <sup>1</sup>                                    | 54 h         |  |  |  |

| × /                      | Waddr               |                 | EE Write P       |                                                       | 58 h         |  |  |  |

| VEE_CTL                  |                     |                 |                  | VEE_Read_Port                                         |              |  |  |  |

|                          |                     |                 |                  |                                                       |              |  |  |  |

| Reserved                 | Reserved            | Reserved        |                  | Reserved                                              | 60 h         |  |  |  |

|                          |                     |                 | Delay Timer      | •                                                     | 64 h         |  |  |  |

#### Table 4. PCI Configuration Register Map

<sup>&</sup>lt;sup>1</sup> WS: If software want to write a power state chip not support, the write cycle will be granted but discarded internally

#### MAC Registers Mapping Table

Listed in the table below are the abbreviations of register access types and its abbreviation implemented for the MAC registers.

| Access<br>Type | Description                    | Access<br>Type | Description                         |

|----------------|--------------------------------|----------------|-------------------------------------|

| RO             | Read only                      | C/S            | Clear or set by Hardware Controller |

| R0             | Read as 0 always               | R              | Can be Read by software.            |

| SC             | Software Driver Control        | W              | Write by software                   |

| HC             | Hardware Control               | W0             | Write "1" clear by software         |

| E              | Updated by EEPROM loading      | W1             | Write "1" set by software           |

| U              | Updated by Hardware Controller |                |                                     |

V

VT6122 provides 256 bytes space range with some page selection in some offset on PCI I/O Map and Memory mapped I/O space, defined in PCI configuration space 10h and 14h. In Windows and gigabit VGHCI, a memory mapped I/O based software is preferred. The I/O space addressing is defined to be 32-bit I/O read/write cycles.

| Offset<br>(Hex) | Byte 3   | Byte 2           | Byte 1               | Byte 0         | Туре  |  |  |  |

|-----------------|----------|------------------|----------------------|----------------|-------|--|--|--|

| 00              | PAR3     | PAR2             | PAR1                 | PAR0           | RW/E  |  |  |  |

| 04              | TCR      | RCR              | PAR5                 | PAR4           | RW/E  |  |  |  |

| 08              | CR3.S    | CR2.s            | CR1.s                | CR0.s          | RW1/E |  |  |  |

| 0C              | CR3.c    | CR2.c            | CR1.c                | CR0.c          | RW0/E |  |  |  |

| 10              | MAR3/CAM | MAR2/CAM         | MAR1/CAM             | MAR0/CAM       |       |  |  |  |

| 14              | MAR7/CAM | MAR6/CAM         | MAR5/CAM             | MAR4/CAM       |       |  |  |  |

| 18              |          | DescBaseAd       | dr.Hi[63:32]         |                | RW    |  |  |  |

| 1C              | Res      | erved            | <b>DataBufBase</b> A | Addr.Hi[63:48] | RW    |  |  |  |

| 20              | RXE_SR   | TXE_SR           | ISR                  | _CTL           |       |  |  |  |

| 24              | ISR3     | ISR2             | ISR1                 | ISR0           | RW0S  |  |  |  |

| 28              | IMR3     | IMR2             | IMR1                 | IMR0           | RW    |  |  |  |

| 2C              |          | TD_STAT          | US_PORT              |                | RW    |  |  |  |

| 30              |          | RDCSR0.s[3:0]    | TDCSR1.s             | TDCSR0.s       | RSU   |  |  |  |

| 34              |          | RDCSR0.c[3:0]    | TDCSR1.c             | TDCSR0.c       | RCU   |  |  |  |

| 38              |          | RDBase0.Lo[31:6] |                      |                |       |  |  |  |

| 3C              | RQETMR   | TQETMR           | RDI                  | NDX            | RWU   |  |  |  |

| 40              |          | TDBase0.         | Lo[31:6]             |                | RW    |  |  |  |

| 44              |          | TDBase1.         | Lo[31:6]             |                | RW    |  |  |  |

| 48              |          | TDBase2          | Lo[31:6]             |                | RW    |  |  |  |

| 4C              |          | TDBase3          | Lo[31:6]             |                | RW    |  |  |  |

| 50              | TDCSI    | ZE[11:0]         | RDC                  | SIZE           | RW    |  |  |  |

| 54              | TDID     | X1[11:0]         | TDIDX                | RCU            |       |  |  |  |

| 58              | TDID     | X3[11:0]         | TDIDX                | X2[11:0]       | RCU   |  |  |  |

| 5C              | RB       | RDU              | Tx Paus              | RW             |       |  |  |  |

| 60              |          | Rese             | rved                 |                |       |  |  |  |

| 64              |          | Rese             | rved                 |                |       |  |  |  |

| 68              | Reserved | Reserved         | CAMCR                | CAMADDR        |       |  |  |  |

| 6C              | Reserved | PHYSR0           | MIISR                | MIICFG         |       |  |  |  |

| 70              | MII DA   | TA PORT          | MIIADR               | MIICR          |       |  |  |  |

| 74              | SOFT     | TIMER 1          | SOFT T               | TIMER 0        | RW    |  |  |  |

| 78              | CFGD     | CFGC             | CFGB                 | CFGA           | RWE   |  |  |  |

| 7C              | MCFG1    | MCFG0            | DCFG1                | DCFG0          | RWE   |  |  |  |

#### VIA Networking Technologies, Inc.

**N**

| Offset<br>(Hex) | Byte 3                          | Byte 2              | Byte 1     | Byte 0     | Туре |  |  |  |  |

|-----------------|---------------------------------|---------------------|------------|------------|------|--|--|--|--|

| 80              | STICKHW                         | PMCPORT             | BISTSR     | BISTCMD    |      |  |  |  |  |

| 84              | Reserved                        | Reserved            | EE_SWDAT   | MIBCR      |      |  |  |  |  |

| 88              | MIB READ PORT                   |                     |            |            |      |  |  |  |  |

| 8C              | BPMD_w Reserved BPMA/EE_WR_DATA |                     |            |            |      |  |  |  |  |

| 90              | EECSR                           | CHKSUM              | BPMD_r     | BPCMD      |      |  |  |  |  |

| 94              | EMBCMD                          | EADDR               | EE_RD_     | DATA       |      |  |  |  |  |

| 98              | MJMPSR                          | Reserved            | CJMPSR     | Reserved   |      |  |  |  |  |

| 9C              | CHIP_GCR                        | DEBUG               | Reserved   | CHIP_GSR   |      |  |  |  |  |

| A0              | WOLCFG.s                        | PWCFG.s             | WOLCR1.s   | WOLCR0.s   | RW1  |  |  |  |  |

| A4              | WOLCFG.c                        | PWCFG.c             | WOLCR1.c   | WOLCR0.c   | RW0  |  |  |  |  |

| A8              | Reser                           | ved                 | WOLSR1.s   | WOLSR0.s   | RW1U |  |  |  |  |

| AC              | Reser                           | ved                 | WOLSR1.c   | WOLSR0.c   | RW0  |  |  |  |  |

| B0              | PATTERN_                        | CRC1[15:0]          | PATTERN_   | CRC0[15:0] | RW   |  |  |  |  |

| B4              | PATTERN_                        | CRC3[15:0]          | PATTERN_   | CRC2[15:0] | RW   |  |  |  |  |

| B8              | PATTERN_                        | CRC5[15:0]          | PATTERN_   | CRC4[15:0] | RW   |  |  |  |  |

| BC              | PATTERN_                        | CRC7[15:0]          | PATTERN_   | CRC6[15:0] | RW   |  |  |  |  |

| C0              |                                 | Pattern 0/4, PTNBMS | K[31:0]    |            | RW   |  |  |  |  |

| C4              |                                 | Pattern 0/4, PTNBMS | K[63:32]   |            | RW   |  |  |  |  |

| C8              |                                 | Pattern 0/4, PTNBMS | K[95:64]   |            | RW   |  |  |  |  |

| CC              |                                 | Pattern 0/4, PTNBMS | K[127:96]  |            | RW   |  |  |  |  |

| D0              |                                 | Pattern 1/5, PTNBMS | K[31:0]    |            | RW   |  |  |  |  |

| D4              |                                 | Pattern 1/5, PTNBMS | K[63:32]   |            | RW   |  |  |  |  |

| D8              |                                 | Pattern 1/5, PTNBMS | K[95:64]   |            | RW   |  |  |  |  |

| DC              |                                 | Pattern 1/5, PTNBMS | K[127:96]  |            | RW   |  |  |  |  |

| E0              |                                 | Pattern 2/6, PTNBMS | K[31:0]    |            | RW   |  |  |  |  |

| E4              |                                 | Pattern 2/6, PTNBMS | K[63:32]   |            | RW   |  |  |  |  |

| E8              |                                 | Pattern 2/6, PTNBMS | K[95:64]   |            | RW   |  |  |  |  |

| EC              |                                 | Pattern 2/6, PTNBMS | K[127:96]  |            | RW   |  |  |  |  |

| F0              |                                 | Pattern 3/7, PTNBMS | K[31:0]    |            | RW   |  |  |  |  |

| F4              |                                 | Pattern 3/7, PTNBMS | K [63:32]  |            | RW   |  |  |  |  |

| F8              |                                 | Pattern 3/7, PTNBMS | K [95:64]  |            | RW   |  |  |  |  |

| FC              |                                 | Pattern 3/7, PTNBMS | K [127:96] |            | RW   |  |  |  |  |

#### MII Register Mapping Table

| Table 5. MII Registers Names & Addresses | Table 5 | . MII Registe | ers Names & | Addresses |

|------------------------------------------|---------|---------------|-------------|-----------|

|------------------------------------------|---------|---------------|-------------|-----------|

| Register Name                           | Register Number | Register Address (Hex) |

|-----------------------------------------|-----------------|------------------------|

| Mode Control                            | 0               | 00                     |

| Mode Status                             | 1               | 01                     |

| PHY Identifier Register #1              | 2               | 02                     |

| PHY Identifier Register #2              | 3               | 03                     |

| Auto-Negotiation Advertisement          | 4               | 04                     |

| Auto-Negotiation Link Partner Ability   | 5               | 05                     |

| Auto-Negotiation Expansion              | 6               | 06                     |

| Auto-Negotiation Next-Page Transmit     | 7               | 07                     |

| Auto Negotiation Link Partner Next Page | 8               | 08                     |

| 1000BASE-T Control                      | 9               | 09                     |

| 1000BASE-T Status                       | 10              | 0A                     |

| Reserved                                | 11              | 0B                     |

| Reserved                                | 12              | 0C                     |

| Reserved                                | 13              | 0D                     |

| Reserved                                | 14              | 0E                     |

| 1000BASE-T Status Extension #1          | 15              | 0F                     |

| 100BASE-TX Status Extension             | 16              | 10                     |

| 1000BASE-T Status Extension #2          | 17              | 11                     |

| Bypass Control                          | 18              | 12                     |

| Receive Error Counter                   | 19              | 13                     |

| False Carrier Sense Counter             | 20              | 14                     |

| Disconnect Counter                      | 21              | 15                     |

| 10BASE-T Control & Status               | 22              | 16                     |

| Extended PHY Control #1                 | 23              | 17                     |

| Extended PHY Control #2                 | 24              | 18                     |

| Interrupt Mask                          | 25              | 19                     |

| Interrupt Status                        | 26              | 1A                     |

| Parallel LED Control                    | 27              | 1B                     |

| Auxiliary Control & Status              | 28              | 1C                     |

| Delay Skew Status                       | 29              | 1D                     |

| Reserved                                | 30              | 1E                     |

| Reserved                                | 31              | 1F                     |

| Register | ter Bit Name      |                                                       |  |  |  |  |  |

|----------|-------------------|-------------------------------------------------------|--|--|--|--|--|

| 18       | Bypass Control R  | egister                                               |  |  |  |  |  |

|          | 6                 | Bypass Non-compliant BCM5400 Detection                |  |  |  |  |  |

|          | 3                 | Parallel-Detect Control                               |  |  |  |  |  |

|          | 1                 | Disable Automatic 1000BASE-T Next-Page Exchange       |  |  |  |  |  |

|          | 0                 | 125MHz Clock Output Enable                            |  |  |  |  |  |

| 22       | 10BASE-T Contro   | ol & Status Register                                  |  |  |  |  |  |

|          | 15                | Link Disable                                          |  |  |  |  |  |

|          | 14                | Jabber Detect Disable                                 |  |  |  |  |  |

|          | 13                | Disable 10BASE-T/100BASE-TX Echo Mode                 |  |  |  |  |  |

|          | 12                | SQE Disable Mode                                      |  |  |  |  |  |

|          | 11:10             | Squelch Control                                       |  |  |  |  |  |

|          | 5:3               | Current Reference Trim                                |  |  |  |  |  |

|          | 2:1               | CRS control                                           |  |  |  |  |  |

| 24       | Extended PHY Co   | ontrol Register #2                                    |  |  |  |  |  |

|          | 15:13             | 100/1000BASE-T Edge Rate Control                      |  |  |  |  |  |