MPC8260UM/D 4/1999 Rev. 0

# MPC8260 PowerQUICC II<sup>™</sup> User's Manual

**PowerPc**<sup>™</sup>

PowerQUICC II, Mfax, and DigitalDNA are trademarks of Motorola, Inc.

The PowerPC name, the PowerPC logotype, PowerPC 601, PowerPC 603, PowerPC 603e, PowerPC 604, PowerPC 604e, and RS/6000 are trademarks of International Business Machines Corporation used by Motorola under license from International Business Machines Corporation. I<sup>2</sup>C is a registered trademark of Philips Semiconductors

Information in this document is provided solely to enable system and software implementers to use PowerPC microprocessors. There are no express or implied copyright licenses granted hereunder to design or fabricate PowerPC integrated circuits or integrated circuits based on the information in this document.

Motorola reserves the right to make changes without further notice to any products herein. Motorola makes no warranty, representation or guarantee regarding the suitability of its products for any particular purpose, nor does Motorola assume any liability arising out of the application or use of any product or circuit, and specifically disclaims any and all liability, including without limitation consequential or incidental damages. "Typical" parameters can and do vary in different applications. All operating parameters, including "Typical" must be validated for each customer application by customer's technical experts. Motorola products are not designed, intended, or authorized for use as components in systems intended for surgical implant into the body, or other applications intended for sustain life, or for any other application, buyer shall hability arising out of the applications, subject for any such unauthorized a publication, Buyer shall indemnify and hold Motorola and its officers, employees, subsidiaries, and distributors harmless against all claims, costs, damages, and expenses, and reasonable attorney fees arising out of directly or indirectly, any claim of personal injury or death associated with such unintended or unauthorized or unauthorized use, even if such claim alleges that Motorola was negligent regarding the design or manufacture of the part.

Motorola and (A) are registered trademarks of Motorola, Inc. Motorola, Inc. is an Equal Opportunity/Affirmative Action Employer.

#### Motorola Literature Distribution Centers:

USA/EUROPE: Motorola Literature Distribution; P.O. Box 5405; Denver, Colorado 80217; Tel.: 1-800-441-2447 or 1-303-675-2140 JAPAN: Nippon Motorola Ltd SPD, Strategic Planning Office 4-32-1, Nishi-Gotanda Shinagawa-ku, Tokyo 141, Japan Tel.: 81-3-5487-8488 ASIA/PACIFC: Motorola Semiconductors H.K. Ltd.; 8B Tai Ping Industrial Park, 51 Ting Kok Road, Tai Po, N.T., Hong Kong; Tel.: 852-26629298

Mfax™: RMFAX0@email.sps.mot.com; TOUCHTONE 1-602-244-6609; US & Canada ONLY (800) 774-1848; World Wide Web Address: http://sps.motorola.com/mfax INTERNET: http://motorola.com/sps

Technical Information: Motorola Inc. SPS Customer Support Center; 1-800-521-6274; electronic mail address: crc@wmkmail.sps.mot.com. Document Comments: FAX (512) 895-2638, Attn: RISC Applications Engineering. World Wide Web Addresses: http://www.mot.com/PowerPC

http://www.mot.com/netcomm http://www.mot.com/HPESD

Overview PowerPC Processor Core Memory Map System Interface Unit (SIU) Reset **External Signals** 60x Signals The 60x Bus Clocks and Power Control Memory Controller Secondary (L2) Cache Support IEEE 1149.1 Test Access Port Communications Processor Module Overview Serial Interface with Time-Slot Assigner CPM Multiplexing **Baud-Rate Generators (BRGs)** Timers SDMA Channels and IDMA Emulation Serial Communications Controllers (SCCs) SCC UART Mode SCC HDLC Mode SCC BISYNC Mode SCC Transparent Mode SCC Ethernet Mode SCC AppleTalk Mode Serial Management Controllers (SMCs) Multi-Channel Controllers (MCCs) Fast Communications Controllers ATM Controller Fast Ethernet Controller FCC HDLC Controller FCC Transparent Controller Serial Peripheral Interface (SPI) I<sup>2</sup>C Controller Parallel I/O Ports **Register Quick Reference Guide** Glossary Index IND

GLO

Overview PowerPC Processor Core Memory Map System Interface Unit (SIU) Reset External Signals 60x Signals The 60x Bus **Clocks and Power Control** Memory Controller Secondary (L2) Cache Support IEEE 1149.1 Test Access Port **Communications Processor Module Overview** Serial Interface with Time-Slot Assigner CPM Multiplexing **Baud-Rate Generators (BRGs)** Timers SDMA Channels and IDMA Emulation Serial Communications Controllers (SCCs) SCC UART Mode SCC HDLC Mode SCC BISYNC Mode SCC Transparent Mode SCC Ethernet Mode SCC AppleTalk Mode Serial Management Controllers (SMCs) Multi-Channel Controllers (MCCs) Fast Communications Controllers **ATM Controller** Fast Ethernet Controller FCC HDLC Controller FCC Transparent Controller Serial Peripheral Interface (SPI) I<sup>2</sup>C Controller Parallel I/O Ports **Register Quick Reference Guide** А GLO Glossary IND Index

1

2

3

4

5

6

7

8

9

10

11

12

13

14

15

16

17

18

19

20

21

22

23

24

25

26

27

28

29

30

31

32

33

34

35

#### Paragraph Number

#### Title

#### Page Number

#### **About This Book**

| Before Using this Manual-Important Note      | lv  |

|----------------------------------------------|-----|

| Audience                                     | lv  |

| Organization                                 | lvi |

| Suggested Reading                            |     |

| MPC8xx Documentation                         |     |

| PowerPC Documentation                        | lix |

| Conventions                                  | lx  |

| Acronyms and Abbreviations                   | lxi |

| PowerPC Architecture Terminology Conventions |     |

#### Chapter 1 Overview

| 1.1     | Features                               |      |

|---------|----------------------------------------|------|

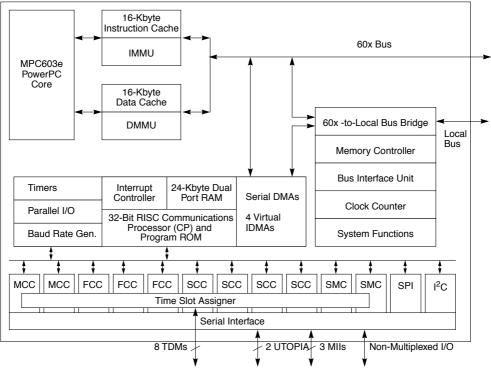

| 1.2     | MPC8260's Architecture Overview        |      |

| 1.2.1   | MPC603e Core                           |      |

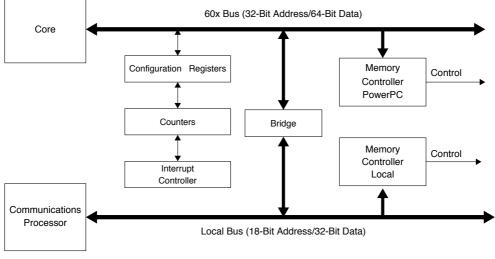

| 1.2.2   | System Interface Unit (SIU)            |      |

| 1.2.3   | Communications Processor Module (CPM)  |      |

| 1.3     | Software Compatibility Issues          | 1-7  |

| 1.3.1   | Signals                                | 1-7  |

| 1.4     | Differences between MPC860 and MPC8260 | 1-9  |

| 1.5     | Serial Protocol Table                  | 1-9  |

| 1.6     | MPC8260 Configurations                 |      |

| 1.6.1   | Pin Configurations                     |      |

| 1.6.2   | Serial Performance                     |      |

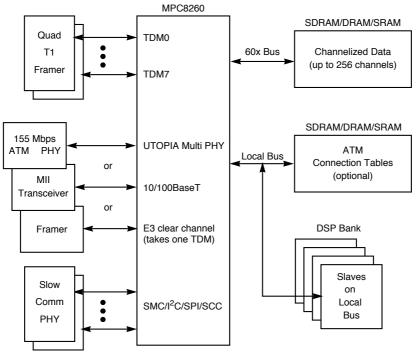

| 1.7     | MPC8260 Application Examples           | 1-11 |

| 1.7.1   | Examples of Communication Systems      |      |

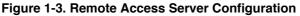

| 1.7.1.1 | Remote Access Server                   | 1-11 |

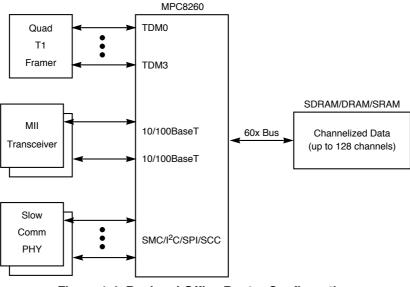

| 1.7.1.2 | Regional Office Router                 |      |

| 1.7.1.3 | LAN-to-WAN Bridge Router               |      |

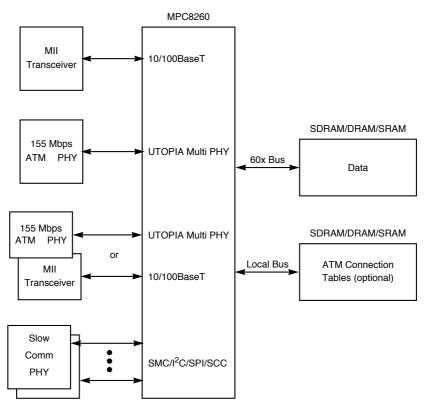

| 1.7.1.4 | Cellular Base Station                  | 1-14 |

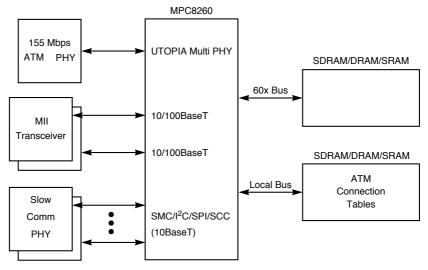

| 1.7.1.5 | Telecommunications Switch Controller   |      |

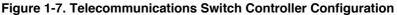

| 1.7.1.6 | SONET Transmission Controller          | 1-15 |

|         |                                        |      |

| Paragraph<br>Number | Title                                  | Page<br>Number |

|---------------------|----------------------------------------|----------------|

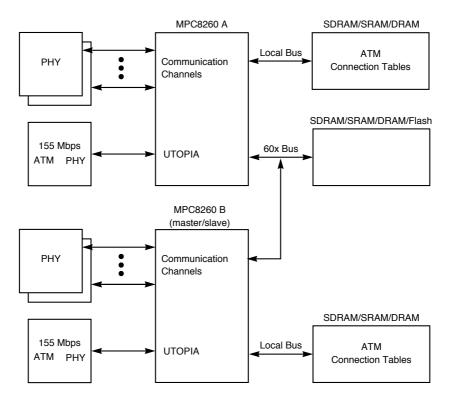

| 1.7.2               | Bus Configurations                     | 1-15           |

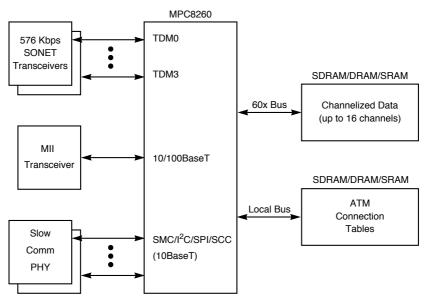

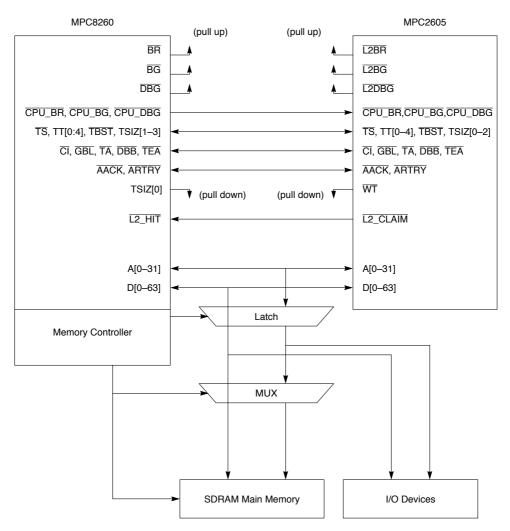

| 1.7.2.1             | Basic System                           | 1-15           |

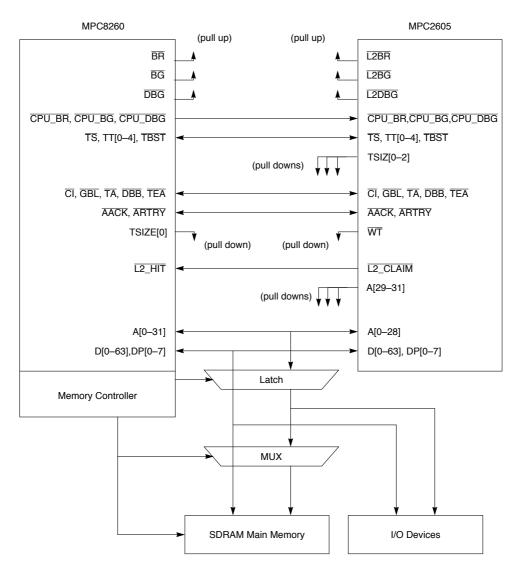

| 1.7.2.2             | High-Performance Communication         | 1-16           |

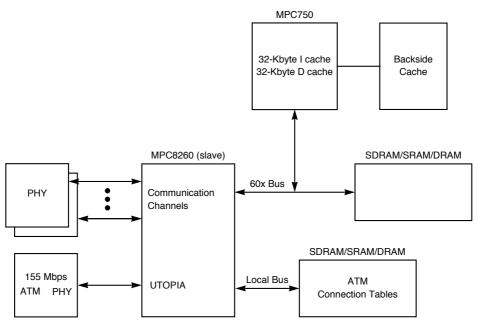

| 1.7.2.3             | High-Performance System Microprocessor | 1-17           |

#### Chapter 2 PowerPC Processor Core

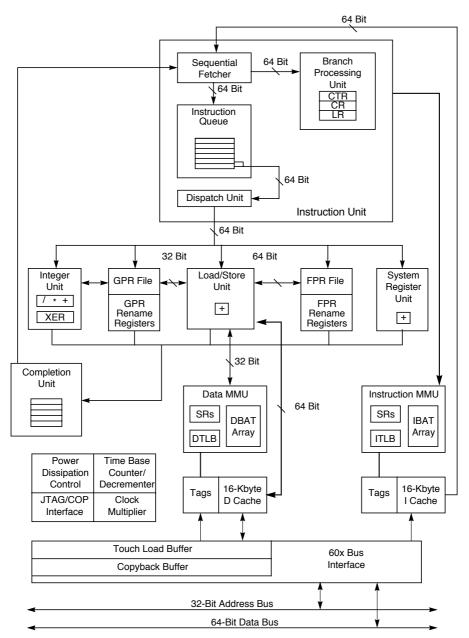

| 2.1       | Overview                                             | 2-1  |

|-----------|------------------------------------------------------|------|

| 2.2       | PowerPC Processor Core Features                      | 2-3  |

| 2.2.1     | Instruction Unit                                     | 2-5  |

| 2.2.2     | Instruction Queue and Dispatch Unit                  | 2-5  |

| 2.2.3     | Branch Processing Unit (BPU)                         | 2-6  |

| 2.2.4     | Independent Execution Units                          | 2-6  |

| 2.2.4.1   | Integer Unit (IU)                                    | 2-6  |

| 2.2.4.2   | Load/Store Unit (LSU)                                | 2-7  |

| 2.2.4.3   | System Register Unit (SRU)                           | 2-7  |

| 2.2.5     | Completion Unit                                      | 2-7  |

| 2.2.6     | Memory Subsystem Support                             |      |

| 2.2.6.1   | Memory Management Units (MMUs)                       | 2-8  |

| 2.2.6.2   | Cache Units                                          | 2-8  |

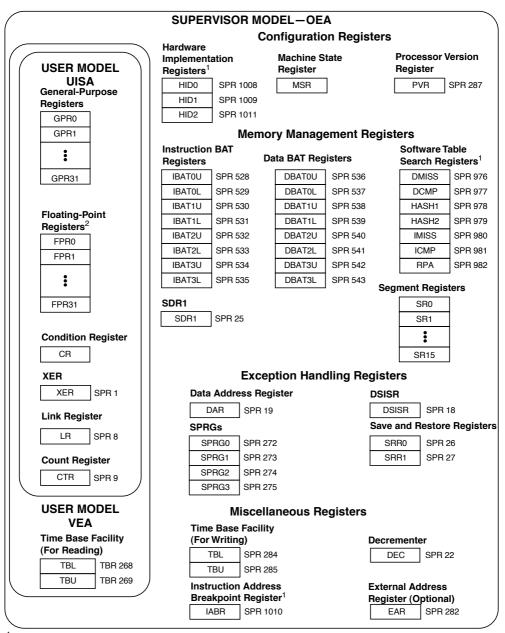

| 2.3       | Programming Model                                    | 2-8  |

| 2.3.1     | Register Set                                         |      |

| 2.3.1.1   | PowerPC Register Set                                 | 2-9  |

| 2.3.1.2   | MPC8260-Specific Registers                           | 2-11 |

| 2.3.1.2.1 | Hardware Implementation-Dependent Register 0 (HID0)  |      |

| 2.3.1.2.2 | Hardware Implementation-Dependent Register 1 (HID1)  | 2-14 |

| 2.3.1.2.3 | Hardware Implementation-Dependent Register 2 (HID2)  | 2-15 |

| 2.3.1.2.4 | Processor Version Register (PVR)                     | 2-16 |

| 2.3.2     | PowerPC Instruction Set and Addressing Modes         | 2-16 |

| 2.3.2.1   | Calculating Effective Addresses                      | 2-16 |

| 2.3.2.2   | PowerPC Instruction Set                              | 2-16 |

| 2.3.2.3   | MPC8260 Implementation-Specific Instruction Set      | 2-18 |

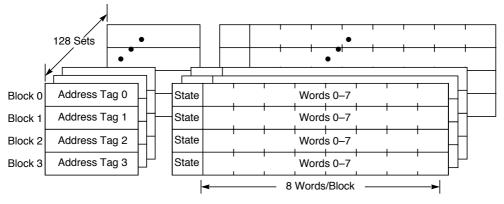

| 2.4       | Cache Implementation                                 |      |

| 2.4.1     | PowerPC Cache Model                                  | 2-18 |

| 2.4.2     | MPC8260 Implementation-Specific Cache Implementation | 2-19 |

| 2.4.2.1   | Data Cache                                           | 2-19 |

| 2.4.2.2   | Instruction Cache                                    | 2-21 |

| 2.4.2.3   | Cache Locking                                        | 2-21 |

| 2.4.2.3.1 | Entire Cache Locking                                 |      |

| 2.4.2.3.2 | Way Locking                                          |      |

| 2.5       | Exception Model                                      |      |

| Paragraph<br>Number | Title                                                       | Page<br>Number |

|---------------------|-------------------------------------------------------------|----------------|

| 2.5.1               | PowerPC Exception Model                                     | 2-22           |

| 2.5.2               | MPC8260 Implementation-Specific Exception Model             | 2-23           |

| 2.5.3               | Exception Priorities                                        | 2-26           |

| 2.6                 | Memory Management                                           | 2-26           |

| 2.6.1               | PowerPC MMU Model                                           |                |

| 2.6.2               | MPC8260 Implementation-Specific MMU Features                | 2-28           |

| 2.7                 | Instruction Timing                                          | 2-29           |

| 2.8                 | Differences between the MPC8260's Core and the PowerPC 603e |                |

|                     | Microprocessor                                              | 2-30           |

#### Chapter 3 Memory Map

#### Chapter 4 System Interface Unit (SIU)

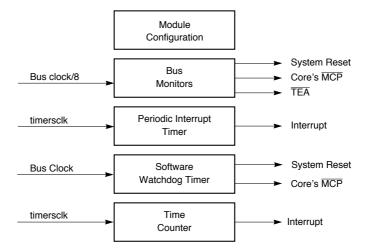

| 4.1     | System Configuration and Protection                    | 4-2  |

|---------|--------------------------------------------------------|------|

| 4.1.1   | Bus Monitor                                            |      |

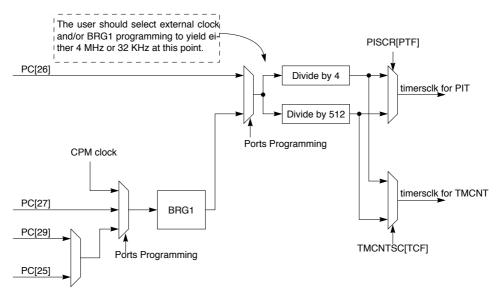

| 4.1.2   | Timers Clock                                           | 4-4  |

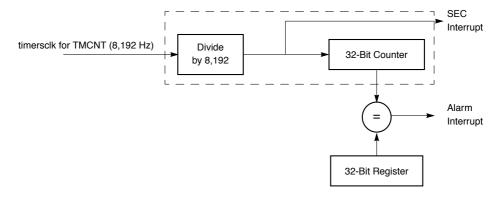

| 4.1.3   | Time Counter (TMCNT)                                   | 4-4  |

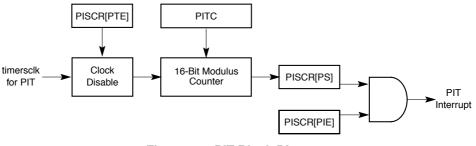

| 4.1.4   | Periodic Interrupt Timer (PIT)                         | 4-5  |

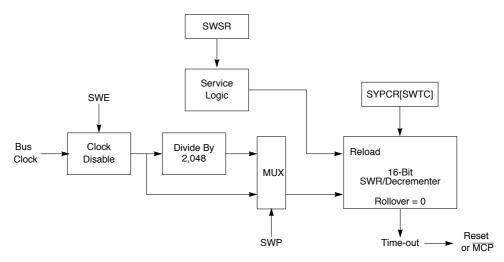

| 4.1.5   | Software Watchdog Timer                                | 4-6  |

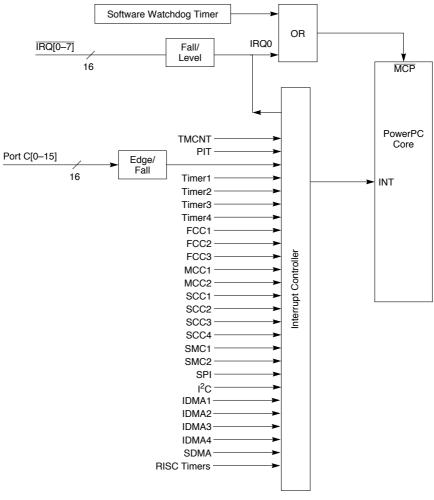

| 4.2     | Interrupt Controller                                   | 4-7  |

| 4.2.1   | Interrupt Configuration                                | 4-8  |

| 4.2.2   | Interrupt Source Priorities                            | 4-9  |

| 4.2.2.1 | SCC, FCC, and MCC Relative Priority                    |      |

| 4.2.2.2 | PIT, TMCNT, and IRQ Relative Priority                  |      |

| 4.2.2.3 | Highest Priority Interrupt                             | 4-13 |

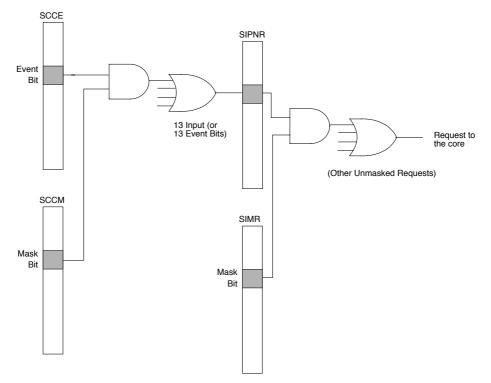

| 4.2.3   | Masking Interrupt Sources                              | 4-13 |

| 4.2.4   | Interrupt Vector Generation and Calculation            | 4-14 |

| 4.2.4.1 | Port C External Interrupts                             | 4-16 |

| 4.3     | Programming Model                                      | 4-17 |

| 4.3.1   | Interrupt Controller Registers                         | 4-17 |

| 4.3.1.1 | SIU Interrupt Configuration Register (SICR)            | 4-17 |

| 4.3.1.2 | SIU Interrupt Priority Register (SIPRR)                | 4-18 |

| 4.3.1.3 | CPM Interrupt Priority Registers (SCPRR_H and SCPRR_L) | 4-19 |

| 4.3.1.4 | SIU Interrupt Pending Registers (SIPNR_H and SIPNR_L)  | 4-21 |

| 4.3.1.5 | SIU Interrupt Mask Registers (SIMR_H and SIMR_L)       |      |

| 4.3.1.6 | SIU Interrupt Vector Register (SIVEC)                  |      |

| 4.3.1.7 | SIU External Interrupt Control Register (SIEXR)        |      |

| 4.3.2   | System Configuration and Protection Registers          |      |

| 4.3.2.1 | Bus Configuration Register (BCR)                       |      |

|         |                                                        |      |

| Paragraph<br>Number | Title Page Number                                                     |

|---------------------|-----------------------------------------------------------------------|

| 4.3.2.2             | 60x Bus Arbiter Configuration Register (PPC_ACR)4-28                  |

| 4.3.2.3             | 60x Bus Arbitration-Level Registers (PPC_ALRH/PPC_ALRL)               |

| 4.3.2.4             | Local Bus Arbiter Configuration Register (LCL_ACR)4-29                |

| 4.3.2.5             | Local Bus Arbitration Level Registers (LCL_ALRH and LCL_ACRL)4-30     |

| 4.3.2.6             | SIU Module Configuration Register (SIUMCR)4-31                        |

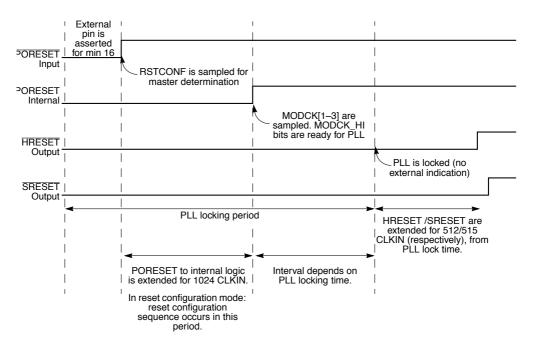

| 4.3.2.7             | Internal Memory Map Register (IMMR)4-34                               |

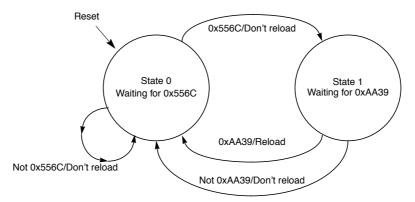

| 4.3.2.8             | System Protection Control Register (SYPCR)                            |

| 4.3.2.9             | Software Service Register (SWSR)4-36                                  |

| 4.3.2.10            | 60x Bus Transfer Error Status and Control Register 1 (TESCR1)4-36     |

| 4.3.2.11            | 60x Bus Transfer Error Status and Control Register 2 (TESCR2)4-37     |

| 4.3.2.12            | Local Bus Transfer Error Status and Control Register 1 (L_TESCR1)4-38 |

| 4.3.2.13            | Local Bus Transfer Error Status and Control Register 2 (L_TESCR2)4-39 |

| 4.3.2.14            | Time Counter Status and Control Register (TMCNTSC)                    |

| 4.3.2.15            | Time Counter Register (TMCNT)                                         |

| 4.3.2.16            | Time Counter Alarm Register (TMCNTAL)4-41                             |

| 4.3.3               | Periodic Interrupt Registers                                          |

| 4.3.3.1             | Periodic Interrupt Status and Control Register (PISCR)                |

| 4.3.3.2             | Periodic Interrupt Timer Count Register (PITC)                        |

| 4.3.3.3             | Periodic Interrupt Timer Register (PITR)4-44                          |

| 4.4                 | SIU Pin Multiplexing4-44                                              |

#### Chapter 5 Reset

| 5.1     | Reset Causes                                 |     |

|---------|----------------------------------------------|-----|

| 5.1.1   | Reset Actions                                | 5-2 |

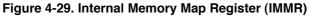

| 5.1.2   | Power-On Reset Flow                          | 5-2 |

| 5.1.3   | HRESET Flow                                  | 5-3 |

| 5.1.4   | SRESET Flow                                  | 5-3 |

| 5.2     | Reset Status Register (RSR)                  | 5-4 |

| 5.3     | Reset Mode Register (RMR)                    | 5-5 |

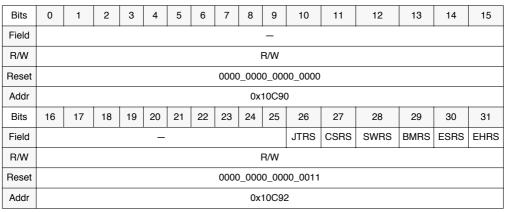

| 5.4     | Reset Configuration                          |     |

| 5.4.1   | Hard Reset Configuration Word                | 5-8 |

| 5.4.2   | Hard Reset Configuration Examples            |     |

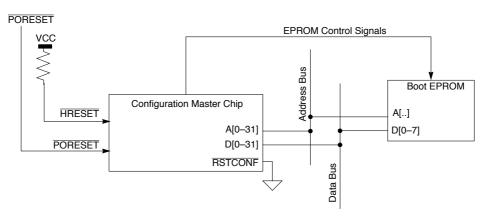

| 5.4.2.1 | Single MPC8260 with Default Configuration    |     |

| 5.4.2.2 | Single MPC8260 Configured from Boot EPROM    |     |

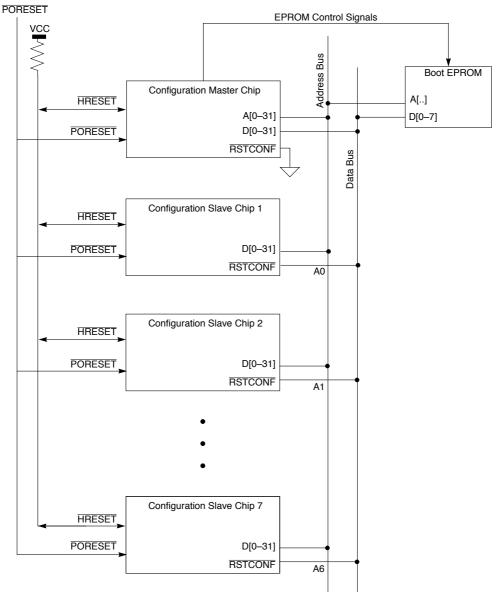

| 5.4.2.3 | Multiple MPC8260s Configured from Boot EPROM |     |

| 5.4.2.4 | Multiple MPC8260s in a System with No EPROM  |     |

|         |                                              |     |

#### Chapter 6

| Paragraph<br>Number | Title            | Page<br>Number |

|---------------------|------------------|----------------|

|                     | External Cignals |                |

#### **External Signals**

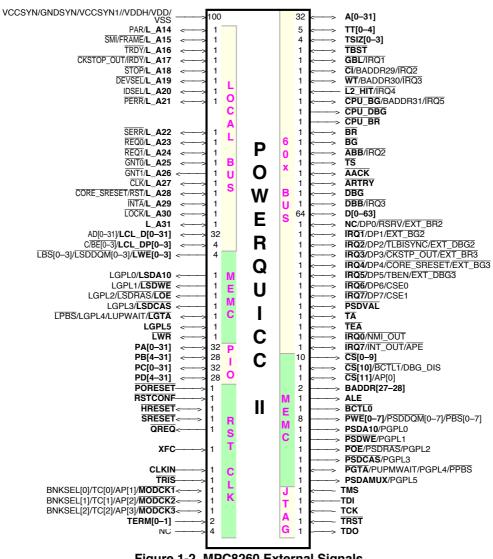

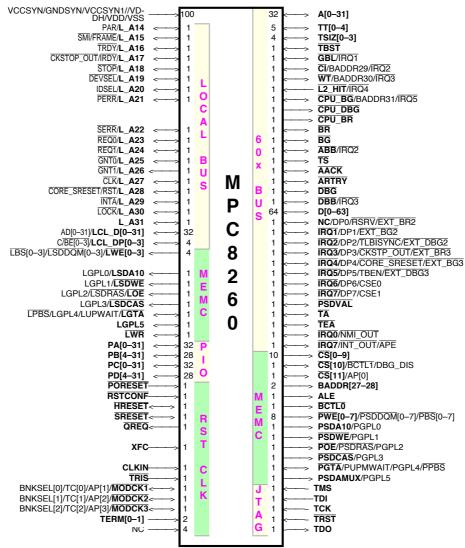

| 6.1 | Functional Pinout   |

|-----|---------------------|

| 6.2 | Signal Descriptions |

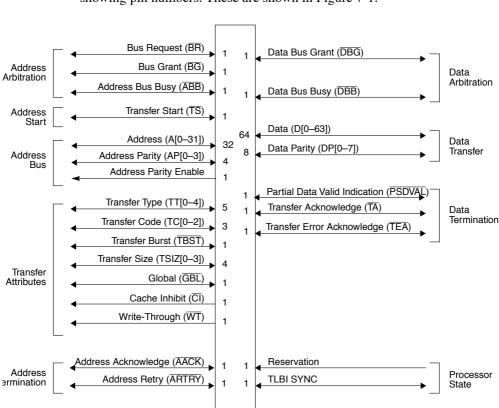

#### Chapter 7 60x Signals

| 7.1       | Signal Configuration                     |

|-----------|------------------------------------------|

| 7.2       | Signal Descriptions                      |

| 7.2.1     | Address Bus Arbitration Signals7-3       |

| 7.2.1.1   | Bus Request (BR)—Output7-3               |

| 7.2.1.1.1 | Address Bus Request (BR)—Output7-3       |

| 7.2.1.1.2 | Address Bus Request (BR)—Input7-4        |

| 7.2.1.2   | Bus Grant (BG)                           |

| 7.2.1.2.1 | Bus Grant (BG)—Input7-4                  |

| 7.2.1.2.2 | Bus Grant (BG)—Output7-5                 |

| 7.2.1.3   | Address Bus Busy (ABB)7-5                |

| 7.2.1.3.1 | Address Bus Busy (ABB)-Output7-5         |

| 7.2.1.3.2 | Address Bus Busy (ABB)—Input7-6          |

| 7.2.2     | Address Transfer Start Signal7-6         |

| 7.2.2.1   | Transfer Start (TS)7-6                   |

| 7.2.2.1.1 | Transfer Start (TS)—Output7-6            |

| 7.2.2.2   | Transfer Start (TS)—Input7-6             |

| 7.2.3     | Address Transfer Signals7-7              |

| 7.2.3.1   | Address Bus (A[0-31])7-7                 |

| 7.2.3.1.1 | Address Bus (A[0-31]) – Output           |

| 7.2.3.1.2 | Address Bus (A[0-31])-Input7-7           |

| 7.2.4     | Address Transfer Attribute Signals7-7    |

| 7.2.4.1   | Transfer Type (TT[0–4])7-8               |

| 7.2.4.1.1 | Transfer Type (TT[0–4])—Output7-8        |

| 7.2.4.1.2 | Transfer Type (TT[0–4])—Input7-8         |

| 7.2.4.2   | Transfer Size (TSIZ[0–3])                |

| 7.2.4.3   | Transfer Burst (TBST)7-8                 |

| 7.2.4.4   | Global (GBL)7-9                          |

| 7.2.4.4.1 | Global (GBL)—Output7-9                   |

| 7.2.4.4.2 | Global (GBL)—Input7-9                    |

| 7.2.4.5   | Caching-Inhibited (CI)—Output7-9         |

| 7.2.4.6   | Write-Through (WT)—Output7-9             |

| 7.2.5     | Address Transfer Termination Signals7-10 |

| 7.2.5.1   | Address Acknowledge (AACK)7-10           |

| 7.2.5.1.1 | Address Acknowledge (AACK)-Output7-10    |

| 7.2.5.1.2 | Address Acknowledge (AACK)—Input7-10     |

| Paragraph<br>Number | Title                                   | Page<br>Number |

|---------------------|-----------------------------------------|----------------|

| 7.2.5.2             | Address Retry (ARTRY)                   | 7-11           |

| 7.2.5.2.1           | Address Retry (ARTRY)—Output            |                |

| 7.2.5.2.2           | Address Retry (ARTRY)-Input             | 7-11           |

| 7.2.6               | Data Bus Arbitration Signals            | 7-12           |

| 7.2.6.1             | Data Bus Grant (DBG)                    |                |

| 7.2.6.1.1           | Data Bus Grant (DBG)—Input              | 7-12           |

| 7.2.6.1.2           | Data Bus Grant (DBG)—Output             | 7-12           |

| 7.2.6.2             | Data Bus Busy (DBB)                     | 7-13           |

| 7.2.6.2.1           | Data Bus Busy (DBB)—Output              | 7-13           |

| 7.2.6.2.2           | Data Bus Busy (DBB)—Input               | 7-13           |

| 7.2.7               | Data Transfer Signals                   | 7-13           |

| 7.2.7.1             | Data Bus (D[0-63])                      |                |

| 7.2.7.1.1           | Data Bus (D[0-63])—Output               | 7-14           |

| 7.2.7.1.2           | Data Bus (D[0-63])—Input                | 7-14           |

| 7.2.7.2             | Data Bus Parity (DP[0-7])               | 7-14           |

| 7.2.7.2.1           | Data Bus Parity (DP[0-7])—Output        | 7-14           |

| 7.2.7.2.2           | Data Bus Parity (DP[0-7])—Input         | 7-15           |

| 7.2.8               | Data Transfer Termination Signals       |                |

| 7.2.8.1             | Transfer Acknowledge (TA)               | 7-15           |

| 7.2.8.1.1           | Transfer Acknowledge (TA)—Input         |                |

| 7.2.8.1.2           | Transfer Acknowledge (TA)—Output        | 7-16           |

| 7.2.8.2             | Transfer Error Acknowledge (TEA)        |                |

| 7.2.8.2.1           | Transfer Error Acknowledge (TEA)—Input  |                |

| 7.2.8.2.2           | Transfer Error Acknowledge (TEA)—Output |                |

| 7.2.8.3             | Partial Data Valid Indication (PSDVAL)  |                |

| 7.2.8.3.1           | Partial Data Valid (PSDVAL)—Input       |                |

| 7.2.8.3.2           | Partial Data Valid (PSDVAL)—Output      | 7-18           |

#### Chapter 8 The 60x Bus

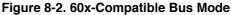

| 8.1   | Terminology                                   | 8-1 |

|-------|-----------------------------------------------|-----|

| 8.2   | Bus Configuration                             | 8-2 |

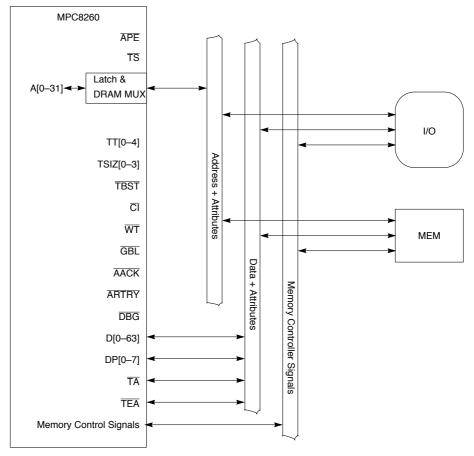

| 8.2.1 | Single MPC8260 Bus Mode                       | 8-2 |

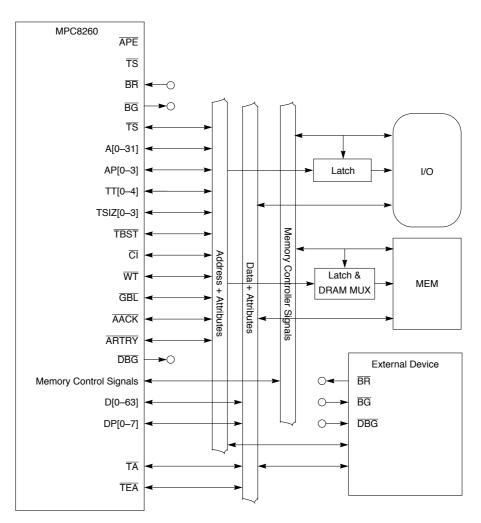

| 8.2.2 | 60x-Compatible Bus Mode                       |     |

| 8.3   | 60x Bus Protocol Overview                     |     |

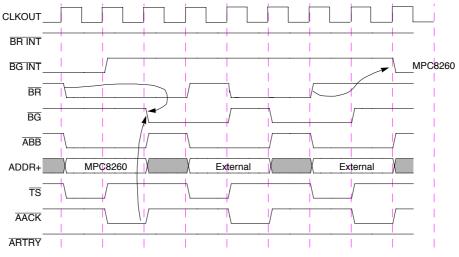

| 8.3.1 | Arbitration Phase                             | 8-5 |

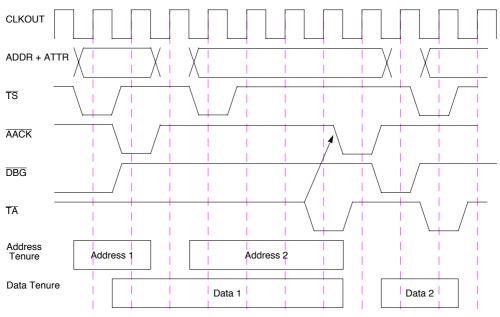

| 8.3.2 | Address Pipelining and Split-Bus Transactions | 8-7 |

| 8.4   | Address Tenure Operations                     | 8-7 |

| 8.4.1 | Address Arbitration                           |     |

| 8.4.2 | Address Pipelining                            | 8-9 |

| 8.4.3 | Address Transfer Attribute Signals            |     |

|       |                                               |     |

| Paragraph<br>Number | Title                                                      | Page<br>Number |

|---------------------|------------------------------------------------------------|----------------|

| 8.4.3.1             | Transfer Type Signal (TT[0-4]) Encoding                    | 8-10           |

| 8.4.3.2             | Transfer Code Signals TC[0–2]                              | 8-13           |

| 8.4.3.3             | TBST and TSIZ[0-3] Signals and Size of Transfer            |                |

| 8.4.3.4             | Burst Ordering During Data Transfers                       | 8-14           |

| 8.4.3.5             | Effect of Alignment on Data Transfers                      |                |

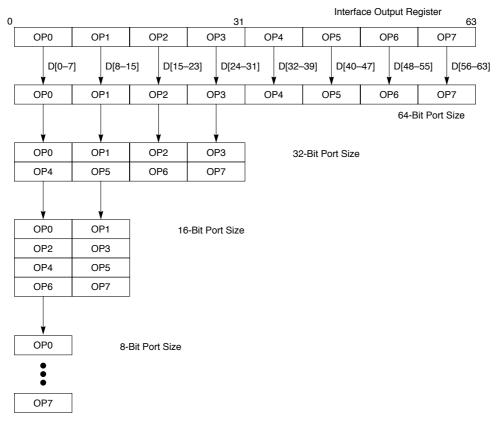

| 8.4.3.6             | Effect of Port Size on Data Transfers                      |                |

| 8.4.3.7             | 60x-Compatible Bus Mode—Size Calculation                   | 8-19           |

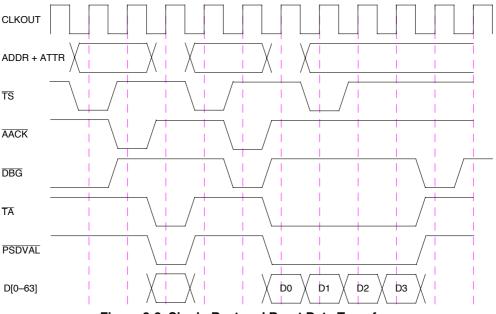

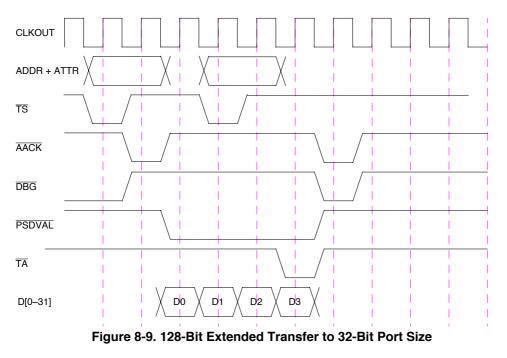

| 8.4.3.8             | Extended Transfer Mode                                     | 8-20           |

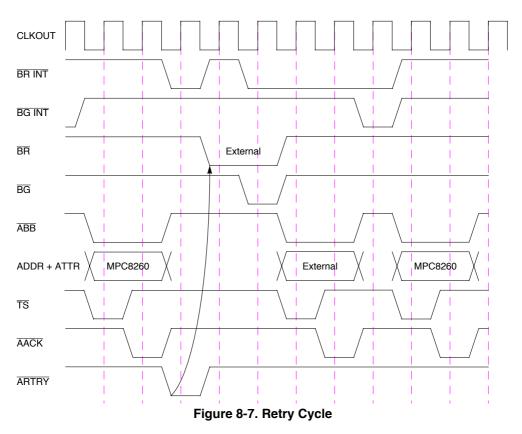

| 8.4.4               | Address Transfer Termination                               | 8-23           |

| 8.4.4.1             | Address Retried with ARTRY                                 | 8-23           |

| 8.4.4.2             | Address Tenure Timing Configuration                        | 8-25           |

| 8.4.5               | Pipeline Control                                           | 8-26           |

| 8.5                 | Data Tenure Operations                                     | 8-26           |

| 8.5.1               | Data Bus Arbitration                                       | 8-26           |

| 8.5.2               | Data Streaming Mode                                        | 8-27           |

| 8.5.3               | Data Bus Transfers and Normal Termination                  | 8-27           |

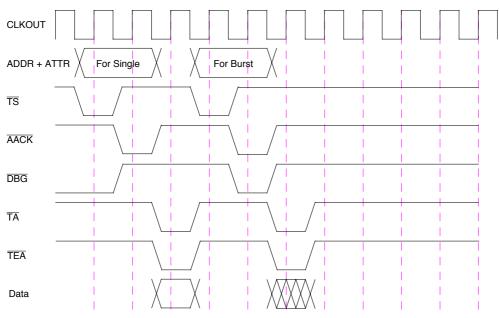

| 8.5.4               | Effect of ARTRY Assertion on Data Transfer and Arbitration | 8-28           |

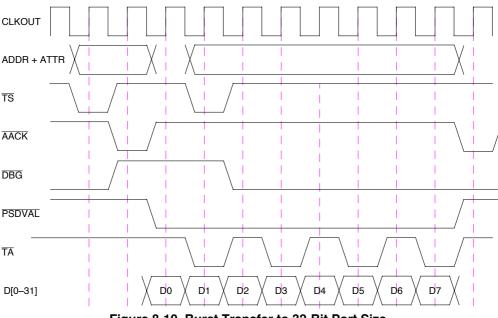

| 8.5.5               | Port Size Data Bus Transfers and PSDVAL Termination        | 8-28           |

| 8.5.6               | Data Bus Termination by Assertion of TEA                   | 8-30           |

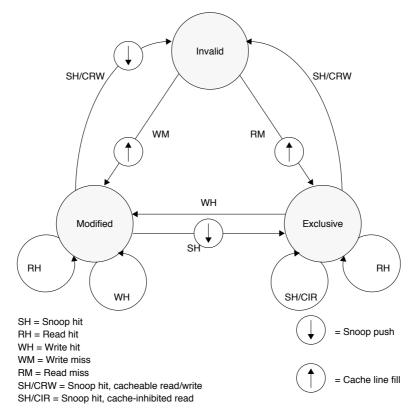

| 8.6                 | Memory Coherency-MEI Protocol                              | 8-31           |

| 8.7                 | Processor State Signals                                    | 8-32           |

| 8.7.1               | Support for the lwarx/stwcx. Instruction Pair              | 8-33           |

| 8.7.2               | TLBISYNC Input                                             | 8-33           |

| 8.8                 | Little-Endian Mode                                         | 8-33           |

#### Chapter 9 Clocks and Power Control

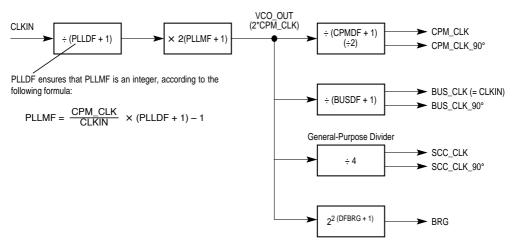

| 9.1   | Clock Unit                           |  |

|-------|--------------------------------------|--|

| 9.2   | Clock Configuration                  |  |

| 9.3   | External Clock Inputs                |  |

| 9.4   | Main PLL                             |  |

| 9.4.1 | PLL Block Diagram                    |  |

| 9.4.2 | Skew Elimination                     |  |

| 9.5   | Clock Dividers                       |  |

| 9.6   | The MPC8260's Internal Clock Signals |  |

| 9.6.1 | General System Clocks                |  |

| 9.7   | PLL Pins                             |  |

|       |                                      |  |

| Paragraph<br>Number | Title                                | Page<br>Number |

|---------------------|--------------------------------------|----------------|

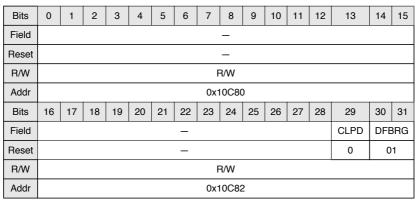

| 9.8                 | System Clock Control Register (SCCR) | 9-8            |

| 9.9                 | System Clock Mode Register (SCMR)    |                |

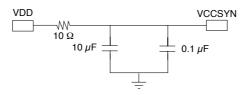

| 9.10                | Basic Power Structure                |                |

#### Chapter 10 Memory Controller

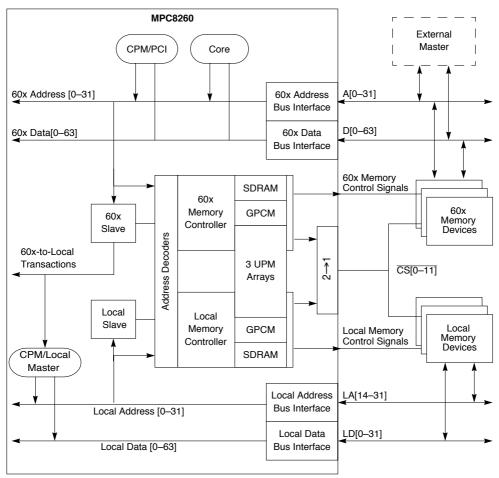

| 10.1    | Features                                                | 10-3  |

|---------|---------------------------------------------------------|-------|

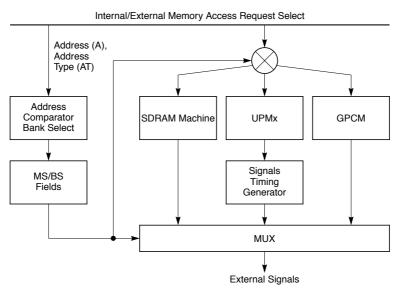

| 10.2    | Basic Architecture                                      | 10-5  |

| 10.2.1  | Address and Address Space Checking                      | 10-8  |

| 10.2.2  | Page Hit Checking                                       | 10-9  |

| 10.2.3  | Error Checking and Correction (ECC)                     |       |

| 10.2.4  | Parity Generation and Checking                          |       |

| 10.2.5  | Transfer Error Acknowledge (TEA) Generation             |       |

| 10.2.6  | Machine Check Interrupt (MCP) Generation                |       |

| 10.2.7  | Data Buffer Controls (BCTLx)                            |       |

| 10.2.8  | Atomic Bus Operation                                    | 10-10 |

| 10.2.9  | Data Pipelining                                         | 10-10 |

| 10.2.10 | External Memory Controller Support                      |       |

| 10.2.11 | External Address Latch Enable Signal (ALE)              |       |

| 10.2.12 | ECC/Parity Byte Select (PBSE)                           | 10-11 |

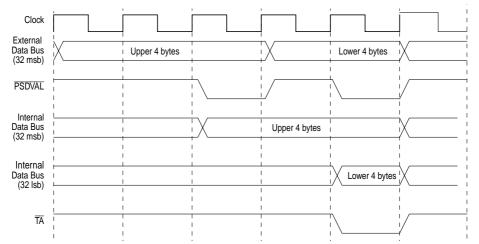

| 10.2.13 | Partial Data Valid Indication (PSDVAL)                  |       |

| 10.3    | Register Descriptions                                   | 10-13 |

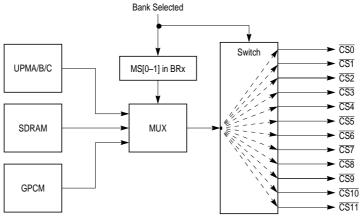

| 10.3.1  | Base Registers (BRx)                                    | 10-14 |

| 10.3.2  | Option Registers (ORx)                                  | 10-16 |

| 10.3.3  | 60x SDRAM Mode Register (PSDMR)                         |       |

| 10.3.4  | Local Bus SDRAM Mode Register (LSDMR)                   |       |

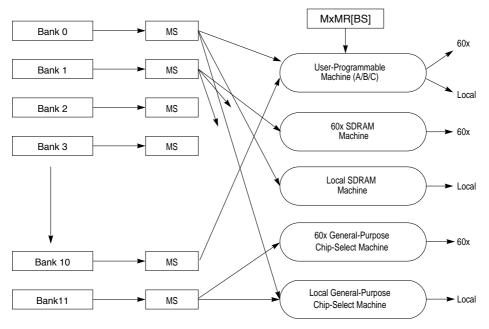

| 10.3.5  | Machine A/B/C Mode Registers (MxMR)                     |       |

| 10.3.6  | Memory Data Register (MDR)                              | 10-28 |

| 10.3.7  | Memory Address Register (MAR)                           |       |

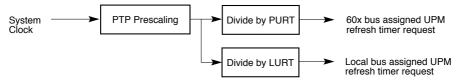

| 10.3.8  | 60x Bus-Assigned UPM Refresh Timer (PURT)               | 10-30 |

| 10.3.9  | Local Bus-Assigned UPM Refresh Timer (LURT)             | 10-30 |

| 10.3.10 | 60x Bus-Assigned SDRAM Refresh Timer (PSRT)             | 10-31 |

| 10.3.11 | Local Bus-Assigned SDRAM Refresh Timer (LSRT)           |       |

| 10.3.12 | Memory Refresh Timer Prescaler Register (MPTPR)         |       |

| 10.3.13 | 60x Bus Error Status and Control Registers (TESCRx)     | 10-33 |

| 10.3.14 | Local Bus Error Status and Control Registers (L_TESCRx) | 10-33 |

| 10.4    | SDRAM Machine                                           | 10-33 |

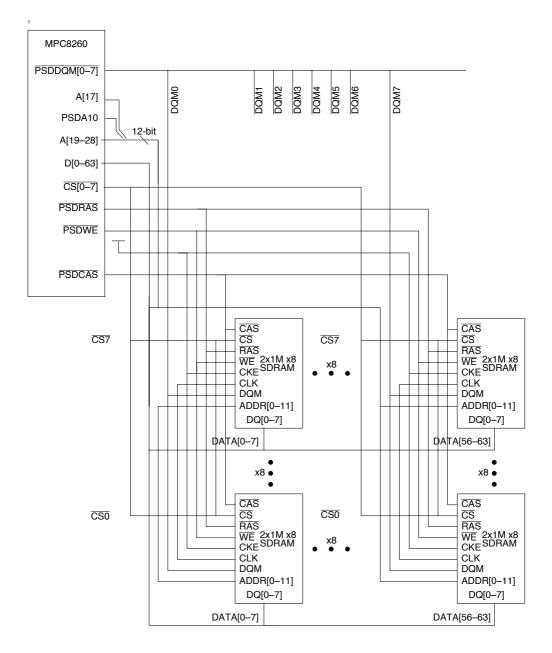

| 10.4.1  | Supported SDRAM Configurations                          | 10-35 |

| 10.4.2  | SDRAM Power-On Initialization                           | 10-35 |

| 10.4.3  | JEDEC-Standard SDRAM Interface Commands                 | 10-35 |

| 10.4.4  | Page-Mode Support and Pipeline Accesses                 |       |

| Paragraph<br>Number | Title                                                 | Page<br>Number |

|---------------------|-------------------------------------------------------|----------------|

| 10.4.5              | Bank Interleaving                                     | 10-36          |

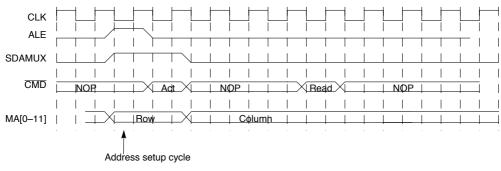

| 10.4.5.1            | SDRAM Address Multiplexing (SDAM and BSMA)            |                |

| 10.4.6              | SDRAM Device-Specific Parameters                      | 10-38          |

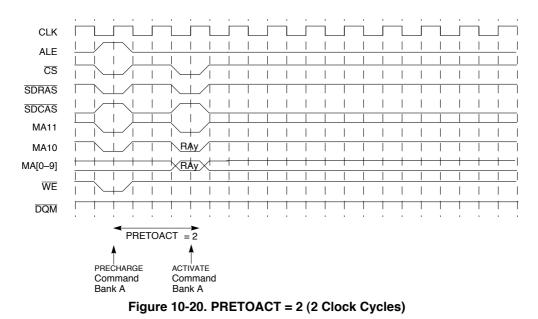

| 10.4.6.1            | Precharge-to-Activate Interval                        |                |

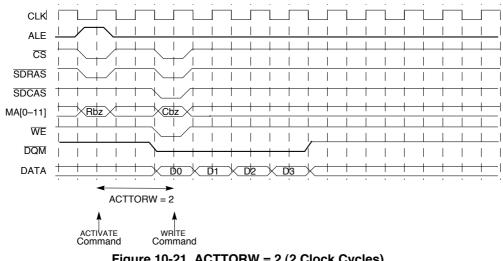

| 10.4.6.2            | Activate to Read/Write Interval                       |                |

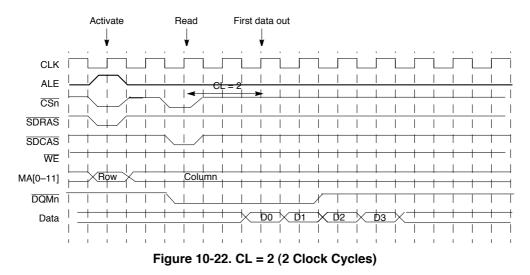

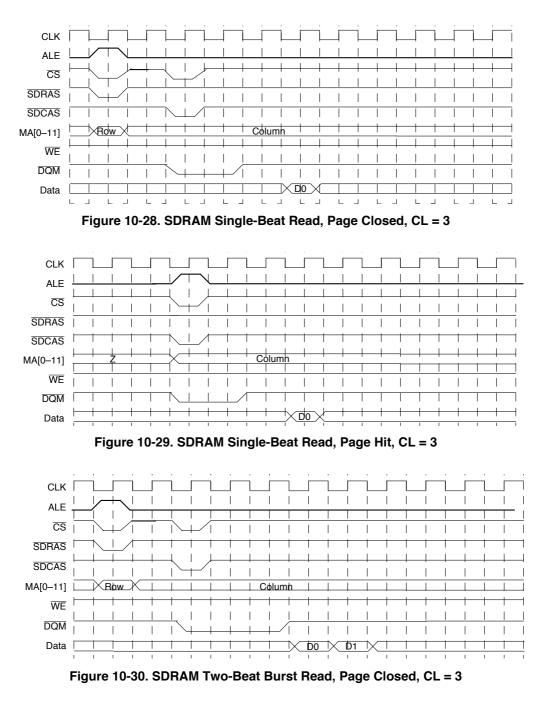

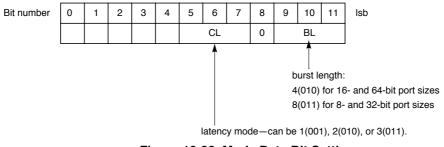

| 10.4.6.3            | Column Address to First Data Out-CAS Latency          | 10-40          |

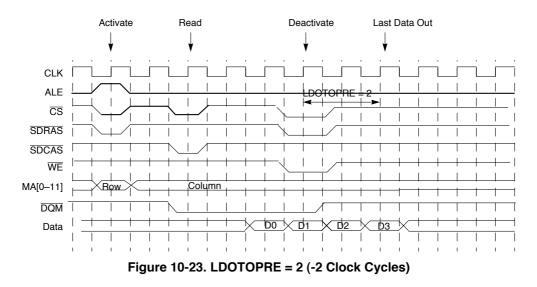

| 10.4.6.4            | Last Data Out to Precharge                            |                |

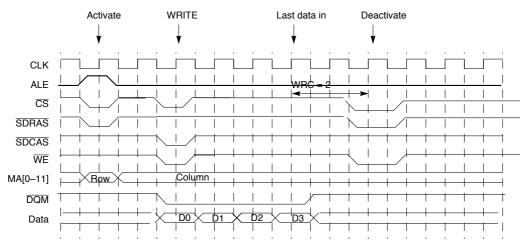

| 10.4.6.5            | Last Data In to Precharge—Write Recovery              | 10-41          |

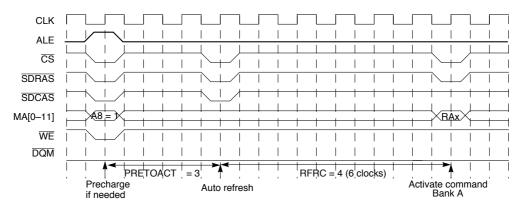

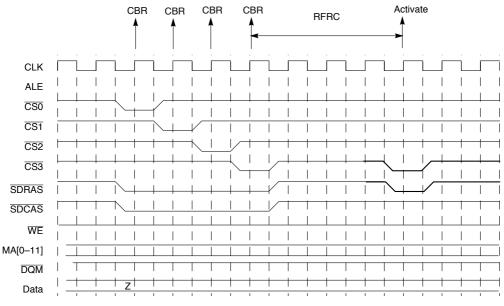

| 10.4.6.6            | Refresh Recovery Interval (RFRC)                      |                |

| 10.4.6.7            | External Address Multiplexing Signal                  | 10-41          |

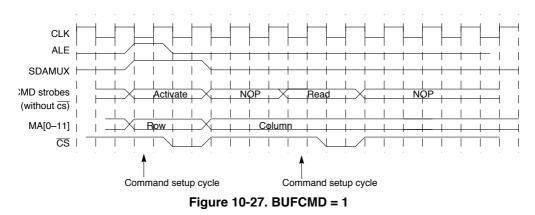

| 10.4.6.8            | External Address and Command Buffers (BUFCMD)         | 10-42          |

| 10.4.7              | SDRAM Interface Timing                                | 10-42          |

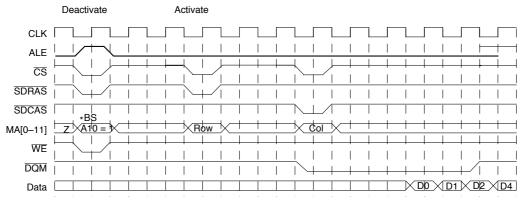

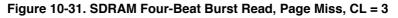

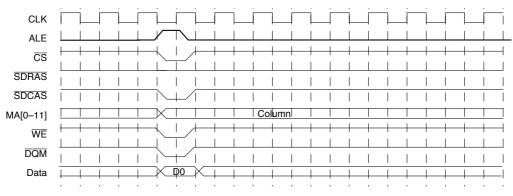

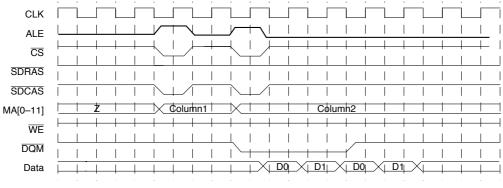

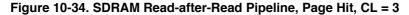

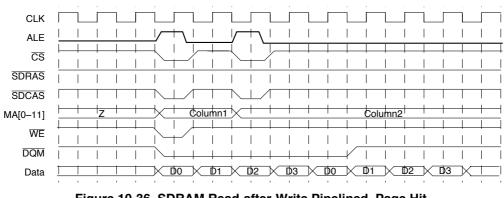

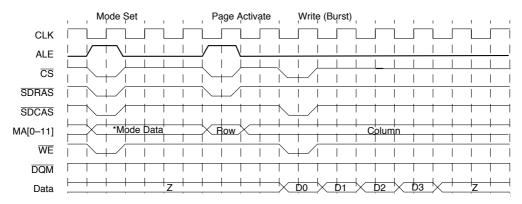

| 10.4.8              | SDRAM Read/Write Transactions                         | 10-46          |

| 10.4.9              | SDRAM Mode-Set Command Timing                         | 10-46          |

| 10.4.10             | SDRAM Refresh                                         | 10-47          |

| 10.4.11             | SDRAM Refresh Timing                                  | 10-47          |

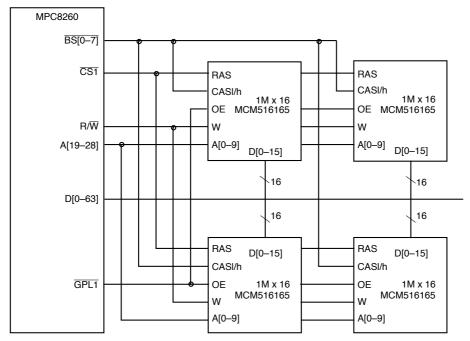

| 10.4.12             | SDRAM Configuration Examples                          | 10-48          |

| 10.4.12.1           | SDRAM Configuration Example (Page-Based Interleaving) | 10-48          |

| 10.4.13             | SDRAM Configuration Example (Bank-Based Interleaving) |                |

| 10.5                | General-Purpose Chip-Select Machine (GPCM)            | 10-51          |

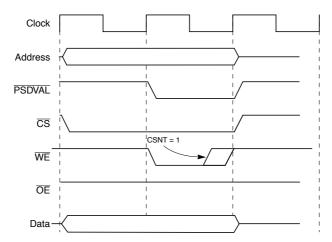

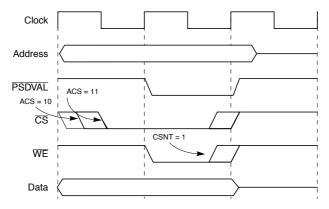

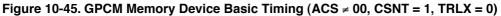

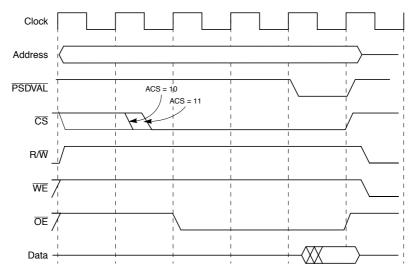

| 10.5.1              | Timing Configuration                                  |                |

| 10.5.1.1            | Chip-Select Assertion Timing                          | 10-53          |

| 10.5.1.2            | Chip-Select and Write Enable Deassertion Timing       | 10-54          |

| 10.5.1.3            | Relaxed Timing                                        |                |

| 10.5.1.4            | Output Enable (OE) Timing                             | 10-57          |

| 10.5.1.5            | Programmable Wait State Configuration                 | 10-57          |

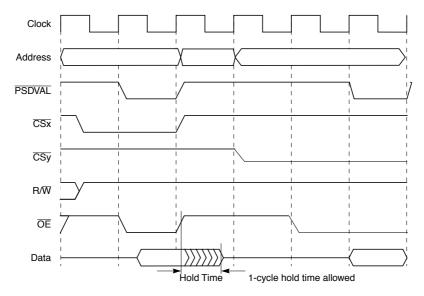

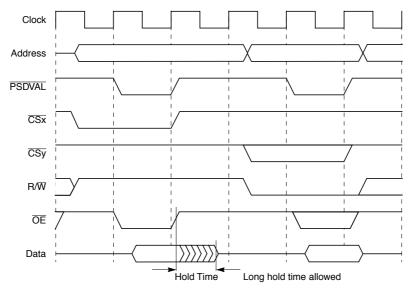

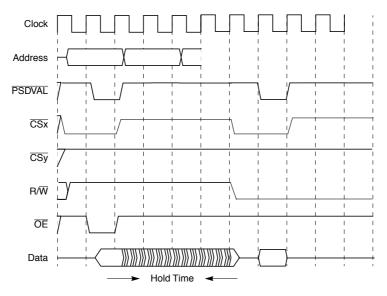

| 10.5.1.6            | Extended Hold Time on Read Accesses                   | 10-57          |

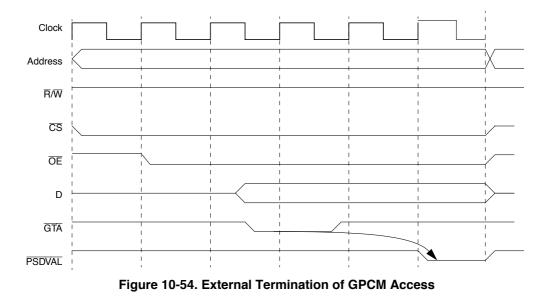

| 10.5.2              | External Access Termination                           | 10-60          |

| 10.5.3              | Boot Chip-Select Operation                            | 10-61          |

| 10.5.4              | Differences between MPC8xx's GPCM and MPC8260's GPCM  |                |

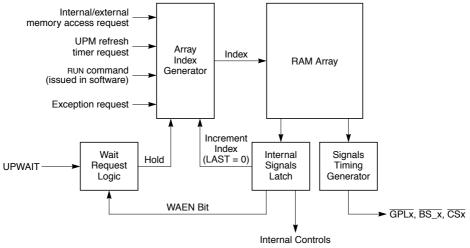

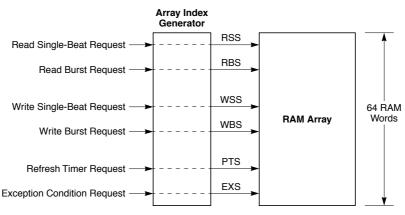

| 10.6                | User-Programmable Machines (UPMs)                     |                |

| 10.6.1              | Requests                                              |                |

| 10.6.1.1            | Memory Access Requests                                | 10-65          |

| 10.6.1.2            | UPM Refresh Timer Requests                            | 10-65          |

| 10.6.1.3            | Software Requests-run Command                         | 10-66          |

| 10.6.1.4            | Exception Requests                                    | 10-66          |

| 10.6.2              | Programming the UPMs                                  | 10-66          |

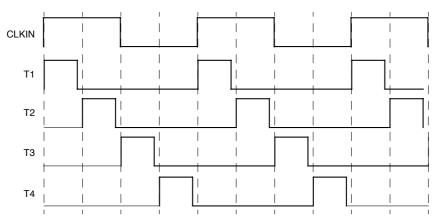

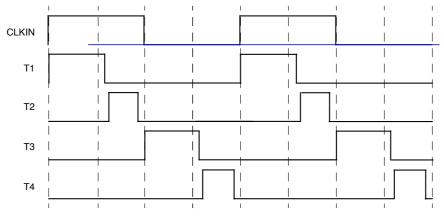

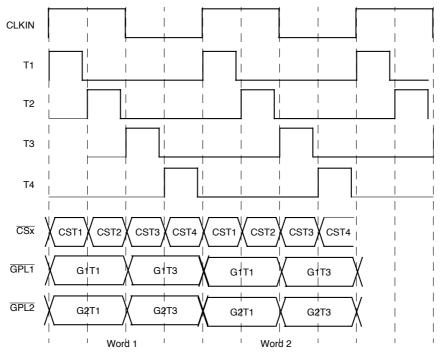

| 10.6.3              | Clock Timing                                          | 10-67          |

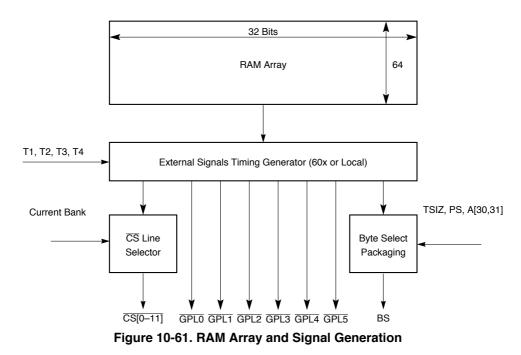

| 10.6.4              | The RAM Array                                         | 10-69          |

| 10.6.4.1            | RAM Words                                             |                |

| 10.6.4.1.1          | Chip-Select Signals (CxTx)                            | 10-74          |

| 10.6.4.1.2          | Byte-Select Signals (BxTx)                            |                |

| 10.6.4.1.3          | General-Purpose Signals (GxTx, GOx)                   | 10-76          |

| Paragraph<br>Number | Title                                               | Page<br>Number |

|---------------------|-----------------------------------------------------|----------------|

| 10.6.4.1.4          | Loop Control                                        |                |

| 10.6.4.1.5          | Repeat Execution of Current RAM Word (REDO)         | 10-76          |

| 10.6.4.2            | Address Multiplexing                                |                |

| 10.6.4.3            | Data Valid and Data Sample Control                  |                |

| 10.6.4.4            | Signals Negation                                    |                |

| 10.6.4.5            | The Wait Mechanism                                  |                |

| 10.6.4.6            | Extended Hold Time on Read Accesses                 |                |

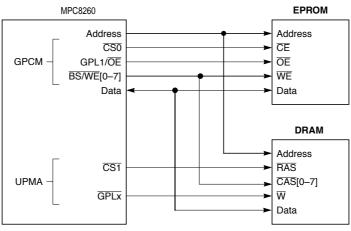

| 10.6.5              | UPM DRAM Configuration Example                      |                |

| 10.6.6              | Differences between MPC8xx UPM and MPC8260 UPM      |                |

| 10.7                | Memory System Interface Example Using UPM           |                |

| 10.7.0.1            | EDO Interface Example                               |                |

| 10.8                | Handling Devices with Slow or Variable Access Times |                |

| 10.8.1              | Hierarchical Bus Interface Example                  |                |

| 10.8.2              | Slow Devices Example                                |                |

| 10.9                | External Master Support (60x-Compatible Mode)       |                |

| 10.9.1              | 60x-Compatible External Masters                     |                |

| 10.9.2              | MPC8260-Type External Masters                       |                |

| 10.9.3              | Extended Controls in 60x-Compatible Mode            |                |

| 10.9.4              | Using BNKSEL SIgnals in Single-MPC8260 Bus Mode     |                |

| 10.9.5              | Address Incrementing for External Bursting Masters  |                |

| 10.9.6              | External Masters Timing                             |                |

| 10.9.6.1            | Example of External Master Using the SDRAM Machine  |                |

#### Chapter 11 Secondary (L2) Cache Support

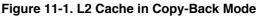

| 11.1   | L2 Cache Configurations                               | 11-1 |

|--------|-------------------------------------------------------|------|

| 11.1.1 | Copy-Back Mode                                        |      |

| 11.1.2 | Write-Through Mode                                    |      |

| 11.1.3 | ECC/Parity Mode                                       |      |

| 11.2   | L2 Cache Interface Parameters                         |      |

| 11.3   | System Requirements When Using the L2 Cache Interface | 11-7 |

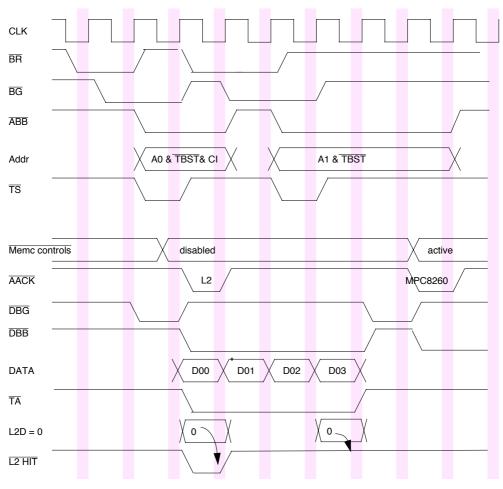

| 11.4   | L2 Cache Operation                                    | 11-7 |

| 11.5   | Timing Example                                        |      |

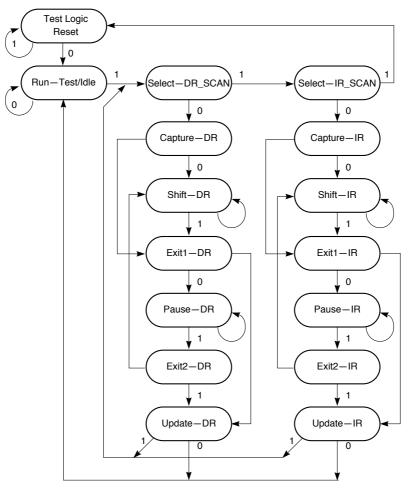

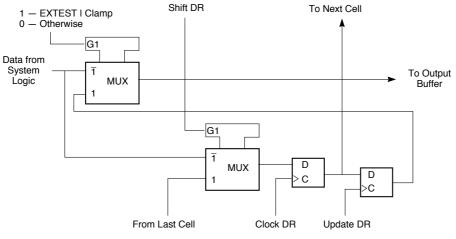

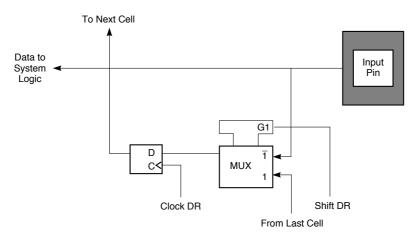

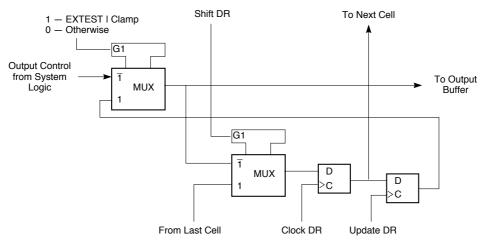

#### Chapter 12 IEEE 1149.1 Test Access Port

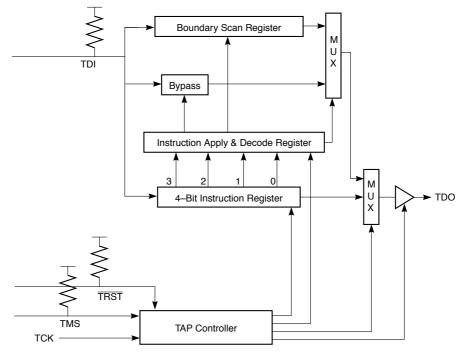

| 12.1 | Overview               |  |

|------|------------------------|--|

| 12.2 | TAP Controller         |  |

| 12.3 | Boundary Scan Register |  |

| 12.4 | Instruction Register   |  |

|      | e                      |  |

| Paragraph<br>Number | Title                   | Page<br>Number |

|---------------------|-------------------------|----------------|

| 12.5                | MPC8260 Restrictions    |                |

| 12.6                | Nonscan Chain Operation |                |

#### Chapter 13 Communications Processor Module Overview

| 13.1     | Features                                              | 13-1  |

|----------|-------------------------------------------------------|-------|

| 13.2     | MPC8260 Serial Configurations                         | 13-3  |

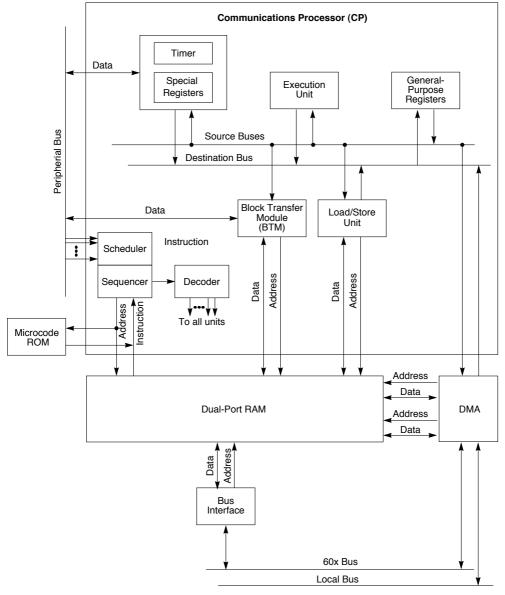

| 13.3     | Communications Processor (CP)                         | 13-4  |

| 13.3.1   | Features                                              | 13-4  |

| 13.3.2   | CP Block Diagram                                      | 13-4  |

| 13.3.3   | PowerPC Core Interface                                | 13-6  |

| 13.3.4   | Peripheral Interface                                  | 13-6  |

| 13.3.5   | Execution from RAM                                    | 13-7  |

| 13.3.6   | RISC Controller Configuration Register (RCCR)         | 13-7  |

| 13.3.7   | RISC Time-Stamp Control Register (RTSCR)              | 13-9  |

| 13.3.8   | RISC Time-Stamp Register (RTSR)                       |       |

| 13.3.9   | RISC Microcode Revision Number                        | 13-10 |

| 13.4     | Command Set                                           |       |

| 13.4.1   | CP Command Register (CPCR)                            | 13-11 |

| 13.4.1.1 | CP Commands                                           |       |

| 13.4.2   | Command Register Example                              | 13-15 |

| 13.4.3   | Command Execution Latency                             | 13-15 |

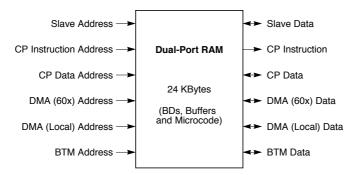

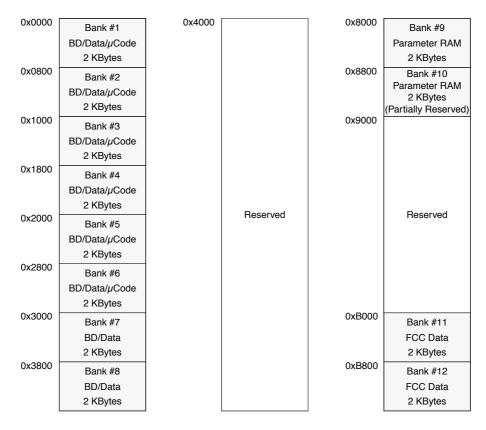

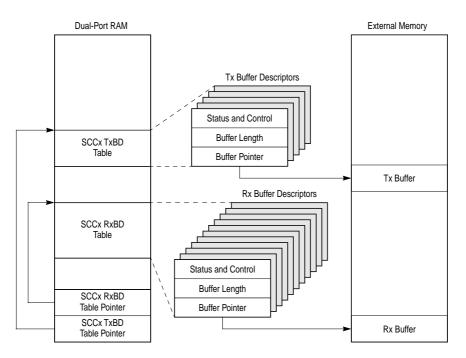

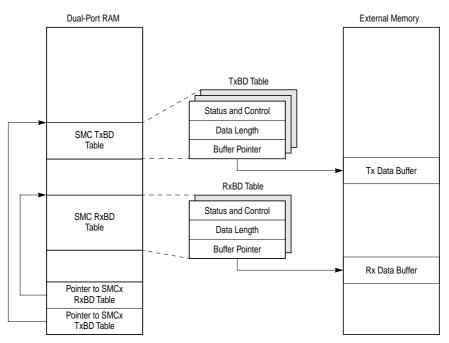

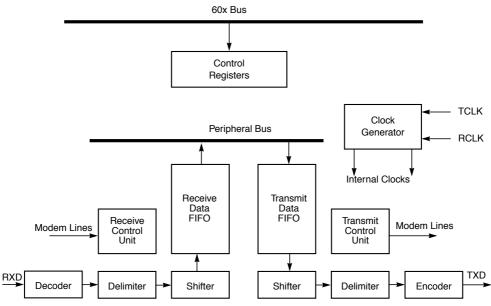

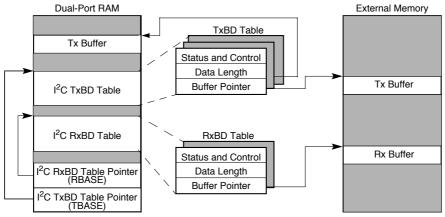

| 13.5     | Dual-Port RAM                                         | 13-15 |

| 13.5.1   | Buffer Descriptors (BDs)                              | 13-17 |

| 13.5.2   | Parameter RAM                                         | 13-17 |

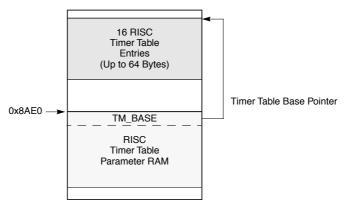

| 13.6     | RISC Timer Tables                                     | 13-18 |

| 13.6.1   | RISC Timer Table Parameter RAM                        | 13-19 |

| 13.6.2   | RISC Timer Command Register (TM_CMD)                  | 13-20 |

| 13.6.3   | RISC Timer Table Entries                              | 13-21 |

| 13.6.4   | RISC Timer Event Register (RTER)/Mask Register (RTMR) | 13-21 |

| 13.6.5   | set timer Command                                     | 13-22 |

| 13.6.6   | RISC Timer Initialization Sequence                    | 13-22 |

| 13.6.7   | RISC Timer Initialization Example                     | 13-22 |

| 13.6.8   | RISC Timer Interrupt Handling                         | 13-23 |

| 13.6.9   | RISC Timer Table Scan Algorithm                       | 13-23 |

| 13.6.10  | Using the RISC Timers to Track CP Loading             | 13-24 |

Paragraph Number

Title

Page Number

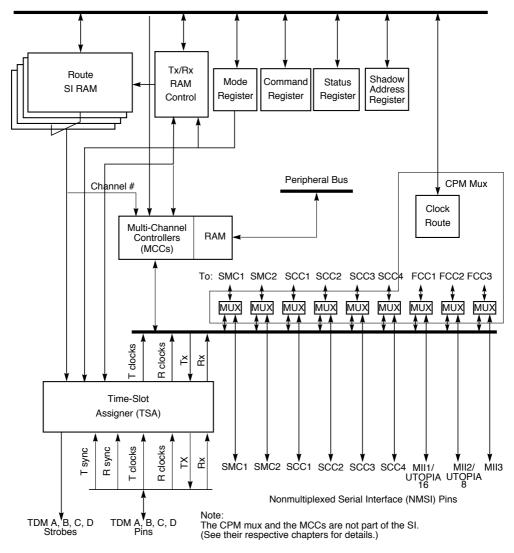

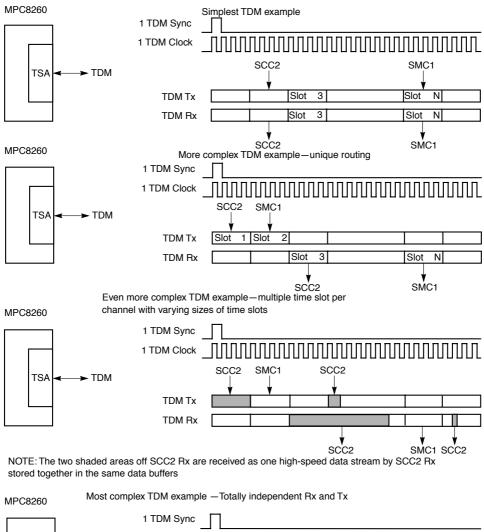

#### Chapter 14 Serial Interface with Time-Slot Assigner

| 14.1     | Features                                    | 14-3  |

|----------|---------------------------------------------|-------|

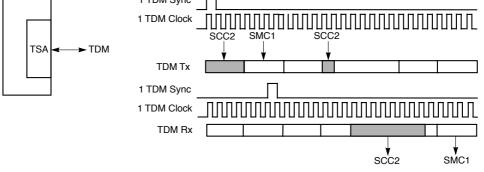

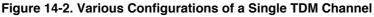

| 14.2     | Overview                                    | 14-4  |

| 14.3     | Enabling Connections to TSA                 | 14-7  |

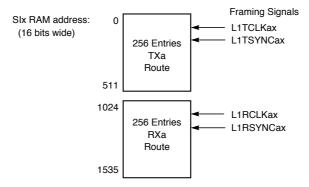

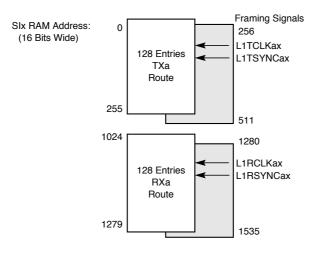

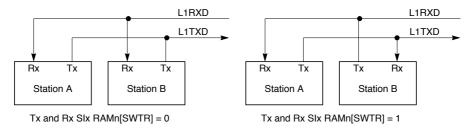

| 14.4     | Serial Interface RAM                        | 14-8  |

| 14.4.1   | One Multiplexed Channel with Static Frames  | 14-9  |

| 14.4.2   | One Multiplexed Channel with Dynamic Frames | 14-9  |

| 14.4.3   | Programming SIx RAM Entries                 | 14-10 |

| 14.4.4   | SIx RAM Programming Example                 | 14-13 |

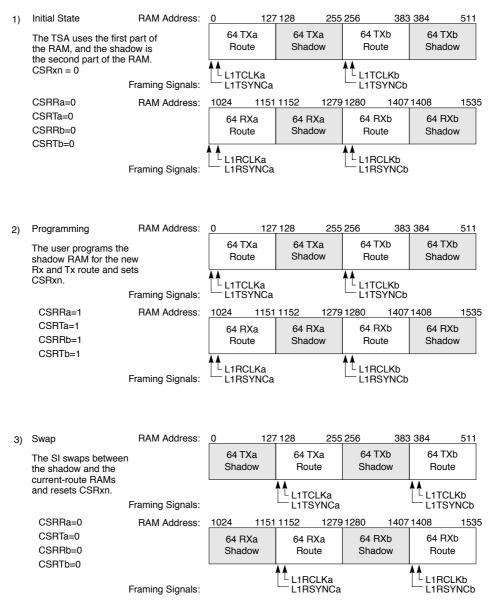

| 14.4.5   | Static and Dynamic Routing                  | 14-14 |

| 14.5     | Serial Interface Registers                  | 14-17 |

| 14.5.1   | SI Global Mode Registers (SIxGMR)           |       |

| 14.5.2   | SI Mode Registers (SIxMR)                   | 14-17 |

| 14.5.3   | SIx RAM Shadow Address Registers (SIxRSR)   |       |

| 14.5.4   | SI Command Register (SIxCMDR)               | 14-24 |

| 14.5.5   | SI Status Registers (SIxSTR)                | 14-25 |

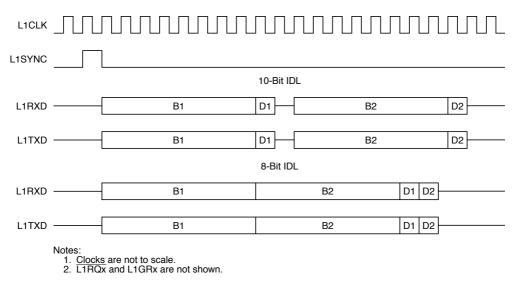

| 14.6     | Serial Interface IDL Interface Support      |       |

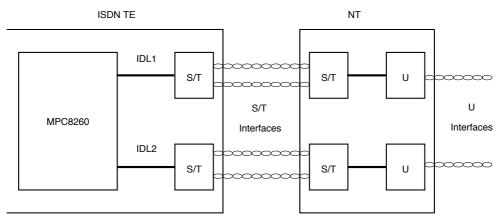

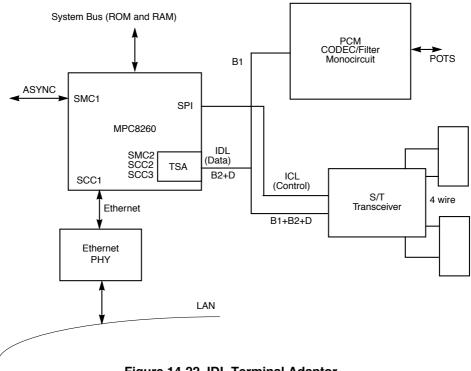

| 14.6.1   | IDL Interface Example                       | 14-26 |

| 14.6.2   | IDL Interface Programming                   |       |

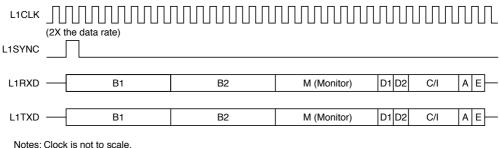

| 14.7     | Serial Interface GCI Support                | 14-31 |

| 14.7.1   | SI GCI Activation/Deactivation Procedure    |       |

| 14.7.2   | Serial Interface GCI Programming            | 14-33 |

| 14.7.2.1 | Normal Mode GCI Programming                 |       |

| 14.7.2.2 | SCIT Programming                            |       |

|          |                                             |       |

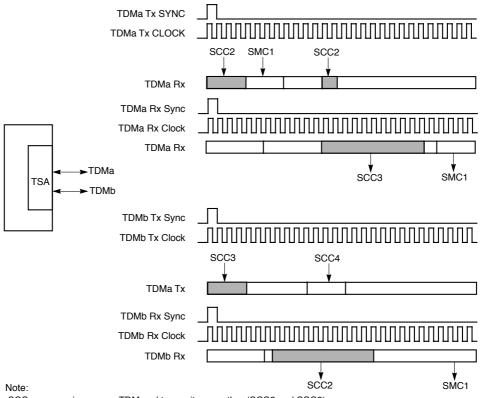

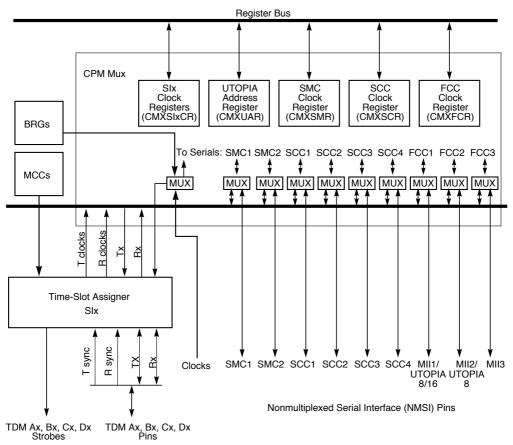

#### Chapter 15 CPM Multiplexing

| 15.1   | Features                                | 15-2  |

|--------|-----------------------------------------|-------|

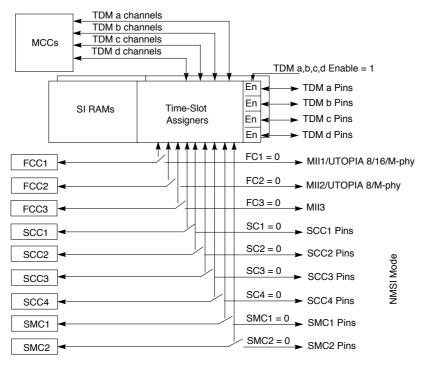

| 15.2   | Enabling Connections to TSA or NMSI     | 15-3  |

| 15.3   | NMSI Configuration                      | 15-4  |

| 15.4   | CMX Registers                           | 15-6  |

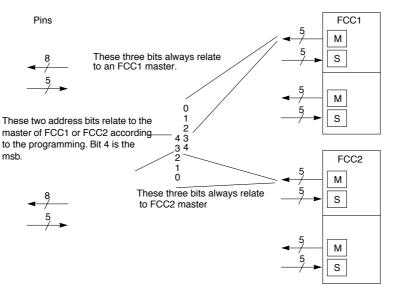

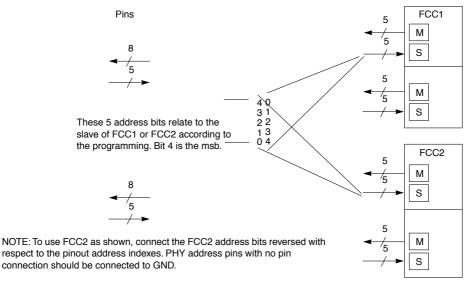

| 15.4.1 | CMX UTOPIA Address Register (CMXUAR)    | 15-7  |

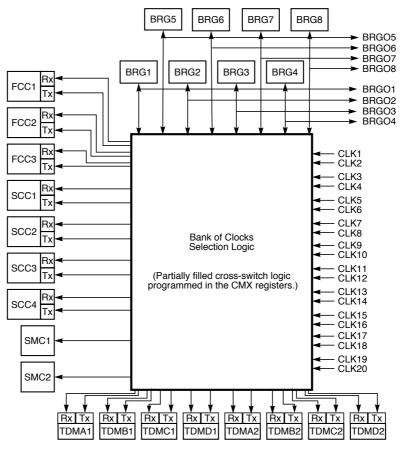

| 15.4.2 | CMX SI1 Clock Route Register (CMXSI1CR) | 15-10 |

| 15.4.3 | CMX SI2 Clock Route Register (CMXSI2CR) | 15-11 |

| 15.4.4 | CMX FCC Clock Route Register (CMXFCR)   | 15-12 |

| 15.4.5 | CMX SCC Clock Route Register (CMXSCR)   | 15-14 |

| 15.4.6 | CMX SMC Clock Route Register (CMXSMR)   | 15-17 |

|        |                                         |       |

| Paragraph |

|-----------|

| Number    |

Title

Page Number

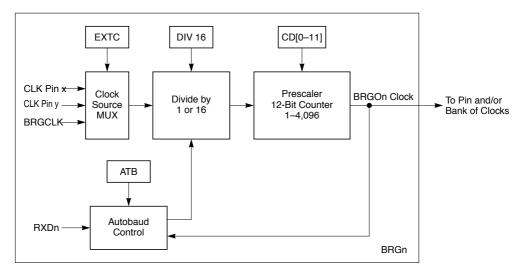

#### Chapter 16 Baud-Rate Generators (BRGs)

| 16.1 | BRG Configuration Registers 1–8 (BRGCx) |  |

|------|-----------------------------------------|--|

| 16.2 | Autobaud Operation on a UART            |  |

| 16.3 | UART Baud Rate Examples                 |  |

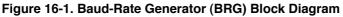

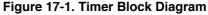

#### Chapter 17 Timers

| 17.1   | Features                                               |  |

|--------|--------------------------------------------------------|--|

| 17.2   | General-Purpose Timer Units                            |  |

| 17.2.1 | Cascaded Mode                                          |  |

| 17.2.2 | Timer Global Configuration Registers (TGCR1 and TGCR2) |  |

| 17.2.3 | Timer Mode Registers (TMR1-TMR4)                       |  |

| 17.2.4 | Timer Reference Registers (TRR1-TRR4)                  |  |

| 17.2.5 | Timer Capture Registers (TCR1-TCR4)                    |  |

| 17.2.6 | Timer Counters (TCN1–TCN4)                             |  |

| 17.2.7 | Timer Event Registers (TER1-TER4)                      |  |

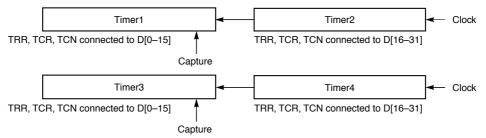

#### Chapter 18 SDMA Channels and IDMA Emulation

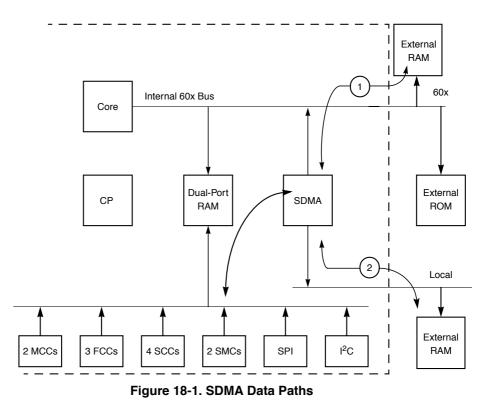

| 18.1 SDMA Bus Arbitration and Bus Transfers                    |       |

|----------------------------------------------------------------|-------|

| 18.2 SDMA Registers                                            |       |

| 18.2.1 SDMA Status Register (SDSR)                             |       |

| 18.2.2 SDMA Mask Register (SDMR)                               | 18-4  |

| 18.2.3 SDMA Transfer Error Address Registers (PDTEA and LDTEA) | 18-4  |

| 18.2.4 SDMA Transfer Error MSNUM Registers (PDTEM and LDTEM)   | 18-4  |

| 18.3 IDMA Emulation                                            |       |

| 18.4 IDMA Features                                             |       |

| 18.5 IDMA Transfers                                            | 18-6  |

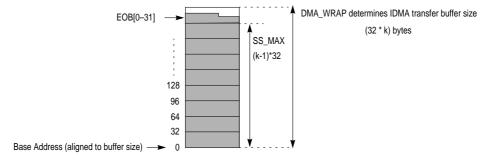

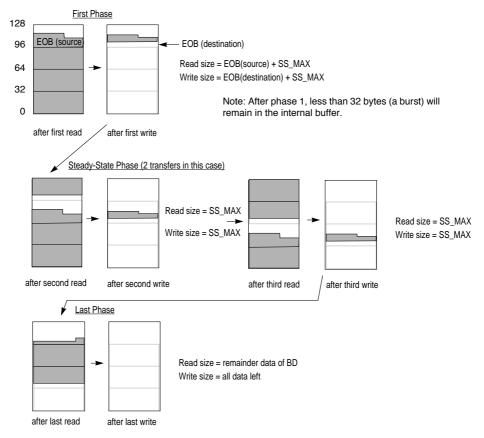

| 18.5.1 Memory-to-Memory Transfers                              | 18-6  |

| 18.5.1.1 External Request Mode                                 | 18-8  |

| 18.5.1.2 Normal Mode                                           | 18-9  |

| 18.5.2 Memory to/from Peripheral Transfers                     | 18-9  |

| 18.5.2.1 Dual-Address Transfers                                | 18-10 |

| 18.5.2.1.1 Peripheral to Memory                                | 18-10 |

| 18.5.2.1.2 Memory to Peripheral                                | 18-10 |

| 18.5.2.2 Single Address (Fly-By) Transfers                     | 18-11 |

| 18.5.2.2.1 Peripheral-to-Memory Fly-By Transfers               | 18-11 |

| 18.5.2.2.2 Memory-to-Peripheral Fly-By Transfers               | 18-11 |

| Paragraph<br>Number | Title Page Number                                             |

|---------------------|---------------------------------------------------------------|

| 18.5.3              | Controlling 60x Bus Bandwidth                                 |

| 18.6                | IDMA Priorities                                               |

| 18.7                | IDMA Interface Signals                                        |

| 18.7.1              | DREQx and DACKx                                               |

| 18.7.1.1            | Level-Sensitive Mode                                          |

| 18.7.1.2            | Edge-Sensitive Mode                                           |

| 18.7.2              | DONEx                                                         |

| 18.8                | IDMA Operation18-14                                           |

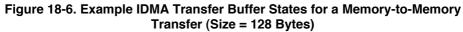

| 18.8.1              | Auto Buffer and Buffer Chaining18-15                          |

| 18.8.2              | IDMAx Parameter RAM18-16                                      |

| 18.8.2.1            | DMA Channel Mode (DCM)18-18                                   |

| 18.8.2.2            | Data Transfer Types as Programmed in DCM18-20                 |

| 18.8.2.3            | Programming DTS and STS18-20                                  |

| 18.8.3              | IDMA Performance                                              |

| 18.8.4              | IDMA Event Register (IDSR) and Mask Register (IDMR)18-22      |

| 18.8.5              | IDMA BDs                                                      |

| 18.9                | IDMA Commands                                                 |

| 18.9.1              | start_idma Command18-26                                       |

| 18.9.2              | stop_idma Command18-26                                        |

| 18.10               | IDMA Bus Exceptions                                           |

| 18.10.1             | Externally Recognizing IDMA Operand Transfers                 |

| 18.11               | Programming the Parallel I/O Registers                        |

| 18.12               | IDMA Programming Examples                                     |

| 18.12.1             | Peripheral-to-Memory Mode (60x Bus to Local Bus)-IDMA218-29   |

| 18.12.2             | Memory-to-Peripheral Fly-By Mode (Both on 60x Bus)-IDMA318-30 |

#### Chapter 19 Serial Communications Controllers (SCCs)

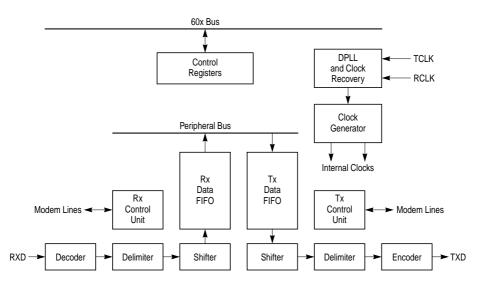

| 19.1     | Features                                     | 19-2  |

|----------|----------------------------------------------|-------|

| 19.1.1   | The General SCC Mode Registers (GSMR1-GSMR4) | 19-3  |

| 19.1.2   | Protocol-Specific Mode Register (PSMR)       | 19-9  |

| 19.1.3   | Data Synchronization Register (DSR)          | 19-9  |

| 19.1.4   | Transmit-on-Demand Register (TODR)           | 19-9  |

| 19.2     | SCC Buffer Descriptors (BDs)                 | 19-10 |

| 19.3     | SCC Parameter RAM                            | 19-13 |

| 19.3.1   | SCC Base Addresses                           | 19-15 |

| 19.3.2   | Function Code Registers (RFCR and TFCR)      | 19-15 |

| 19.3.3   | Handling SCC Interrupts                      | 19-16 |

| 19.3.4   | Initializing the SCCs                        | 19-17 |

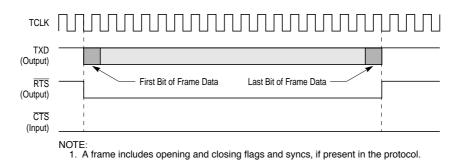

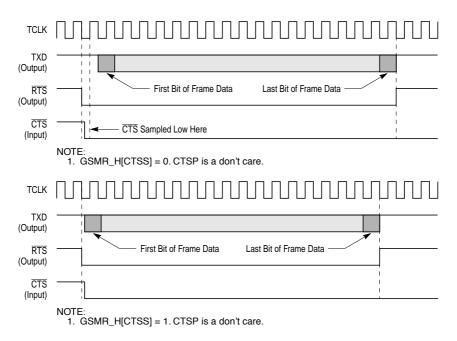

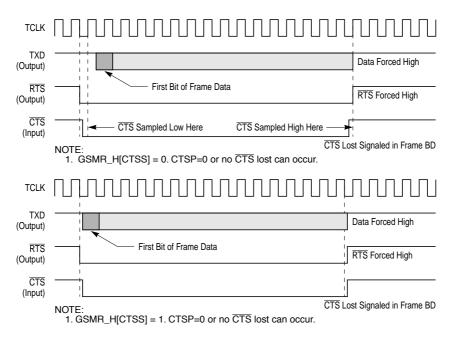

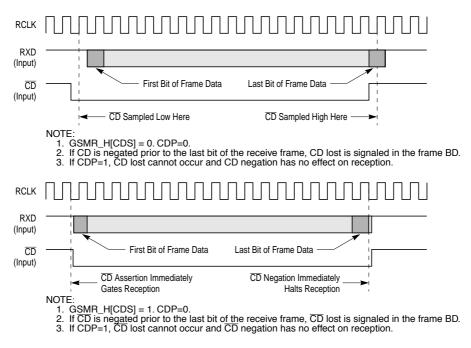

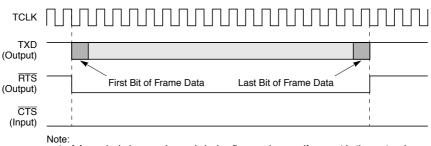

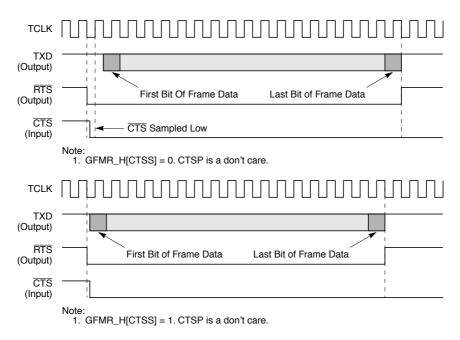

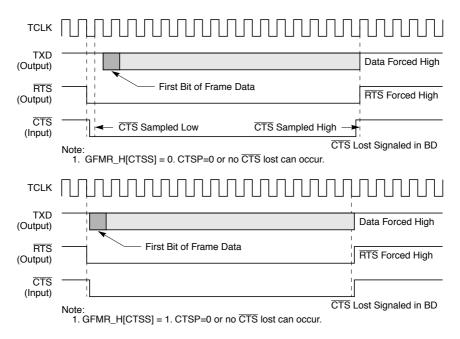

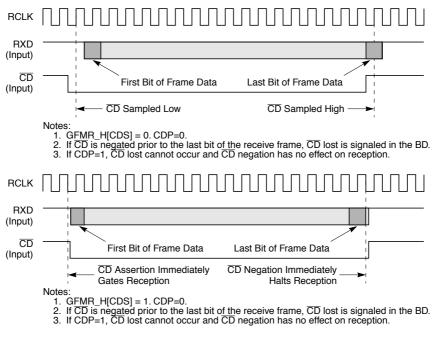

| 19.3.5   | Controlling SCC Timing with RTS, CTS, and CD |       |

| 19.3.5.1 | Synchronous Protocols                        |       |

| Paragraph<br>Number | Title                                                   | Page<br>Number |

|---------------------|---------------------------------------------------------|----------------|

| 19.3.5.2            | Asynchronous Protocols                                  |                |

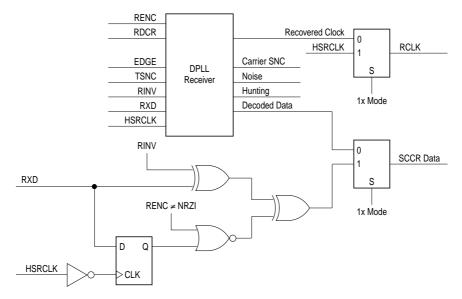

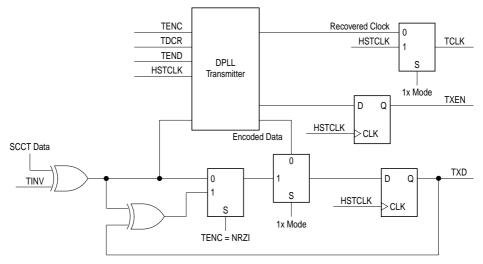

| 19.3.6              | Digital Phase-Locked Loop (DPLL) Operation              |                |

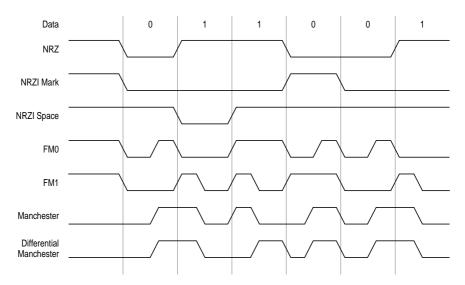

| 19.3.6.1            | Encoding Data with a DPLL                               |                |

| 19.3.7              | Clock Glitch Detection                                  | 19-26          |

| 19.3.8              | Reconfiguring the SCCs                                  | 19-26          |

| 19.3.8.1            | General Reconfiguration Sequence for an SCC Transmitter | 19-26          |

| 19.3.8.2            | Reset Sequence for an SCC Transmitter                   | 19-27          |

| 19.3.8.3            | General Reconfiguration Sequence for an SCC Receiver    |                |

| 19.3.8.4            | Reset Sequence for an SCC Receiver                      | 19-27          |

| 19.3.8.5            | Switching Protocols                                     | 19-27          |

| 19.3.9              | Saving Power                                            |                |

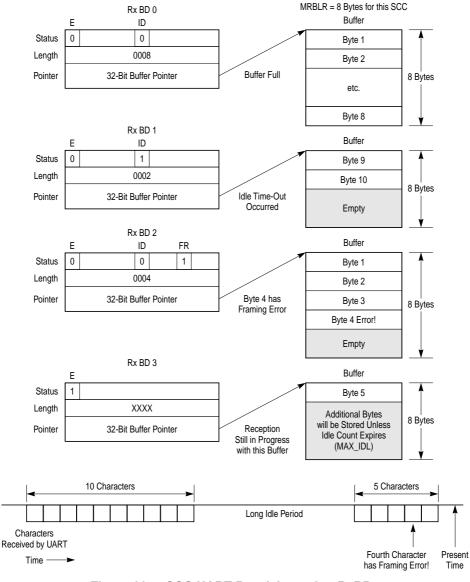

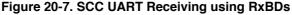

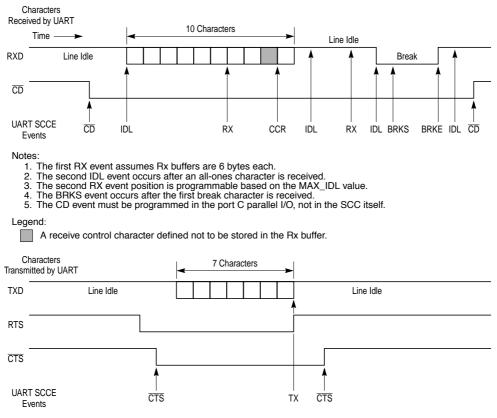

#### Chapter 20 SCC UART Mode

| 20.1  | Features                                                   |  |

|-------|------------------------------------------------------------|--|

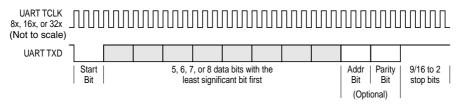

| 20.2  | Normal Asynchronous Mode                                   |  |

| 20.3  | Synchronous Mode                                           |  |

| 20.4  | SCC UART Parameter RAM                                     |  |

| 20.5  | Data-Handling Methods: Character- or Message-Based         |  |

| 20.6  | Error and Status Reporting                                 |  |

| 20.7  | SCC UART Commands                                          |  |

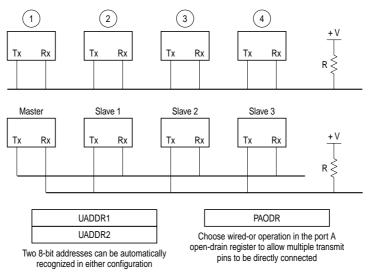

| 20.8  | Multidrop Systems and Address Recognition                  |  |

| 20.9  | Receiving Control Characters                               |  |

| 20.10 | Hunt Mode (Receiver)                                       |  |

| 20.11 | Inserting Control Characters into the Transmit Data Stream |  |

| 20.12 | Sending a Break (Transmitter)                              |  |

| 20.13 | Sending a Preamble (Transmitter)                           |  |

| 20.14 | Fractional Stop Bits (Transmitter)                         |  |

| 20.15 | Handling Errors in the SCC UART Controller                 |  |

| 20.16 | UART Mode Register (PSMR)                                  |  |

| 20.17 | SCC UART Receive Buffer Descriptor (RxBD)                  |  |

| 20.18 | SCC UART Transmit Buffer Descriptor (TxBD)                 |  |

| 20.19 | SCC UART Event Register (SCCE) and Mask Register (SCCM)    |  |

| 20.20 | SCC UART Status Register (SCCS)                            |  |

| 20.21 | SCC UART Programming Example                               |  |

| 20.22 | S-Records Loader Application                               |  |

|       |                                                            |  |

Paragraph Number

Title

#### Page Number

#### Chapter 21 SCC HDLC Mode

| 21.1      | SCC HDLC Features                                    | 21-2  |

|-----------|------------------------------------------------------|-------|

| 21.2      | SCC HDLC Channel Frame Transmission                  |       |

| 21.3      | SCC HDLC Channel Frame Reception                     |       |

| 21.4      | SCC HDLC Parameter RAM                               |       |

| 21.5      | Programming the SCC in HDLC Mode                     |       |

| 21.6      | SCC HDLC Commands                                    | 21-5  |

| 21.7      | Handling Errors in the SCC HDLC Controller           | 21-6  |

| 21.8      | HDLC Mode Register (PSMR)                            | 21-7  |

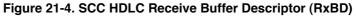

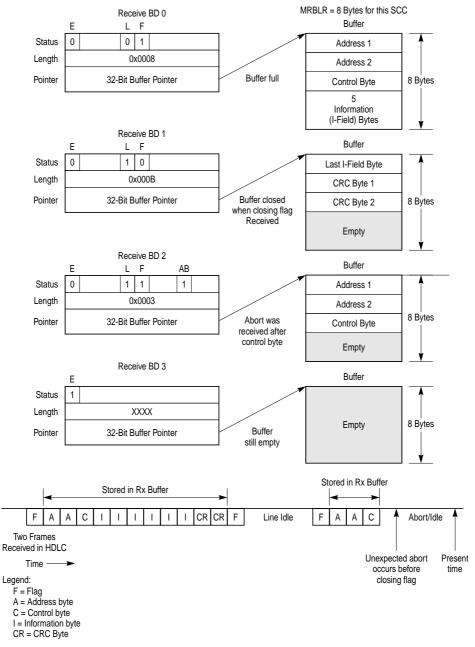

| 21.9      | SCC HDLC Receive Buffer Descriptor (RxBD)            | 21-8  |

| 21.10     | SCC HDLC Transmit Buffer Descriptor (TxBD)           | 21-11 |

| 21.11     | HDLC Event Register (SCCE)/HDLC Mask Register (SCCM) | 21-12 |

| 21.12     | SCC HDLC Status Register (SCCS)                      |       |

| 21.13     | SCC HDLC Programming Examples                        | 21-14 |

| 21.13.1   | SCC HDLC Programming Example #1                      | 21-15 |

| 21.13.2   | SCC HDLC Programming Example #2                      |       |

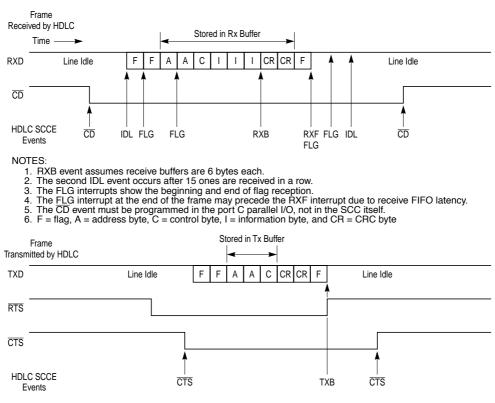

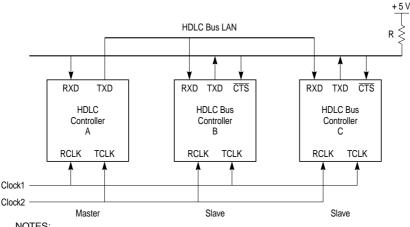

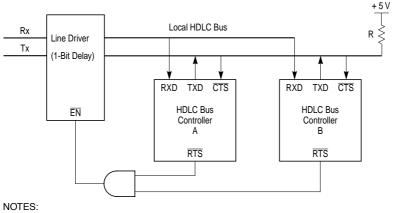

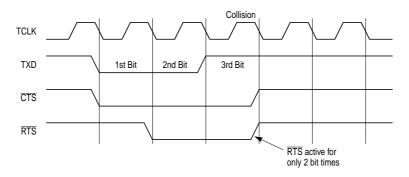

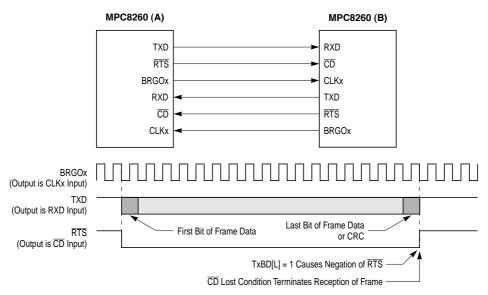

| 21.14     | HDLC Bus Mode with Collision Detection               | 21-17 |

| 21.14.1   | HDLC Bus Features                                    | 21-19 |

| 21.14.2   | Accessing the HDLC Bus                               | 21-19 |

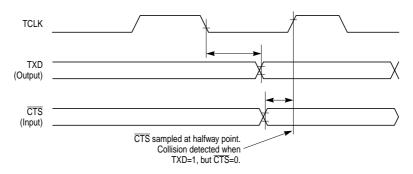

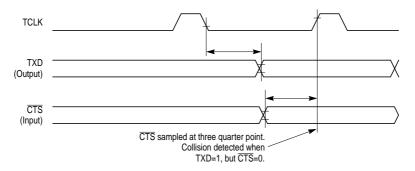

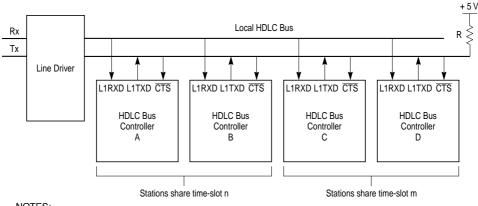

| 21.14.3   | Increasing Performance                               |       |

| 21.14.4   | Delayed RTS Mode                                     | 21-21 |

| 21.14.5   | Using the Time-Slot Assigner (TSA)                   |       |

| 21.14.6   | HDLC Bus Protocol Programming                        |       |

| 21.14.6.1 | Programming GSMR and PSMR for the HDLC Bus Protocol  |       |

| 21.14.6.2 | HDLC Bus Controller Programming Example              |       |

|           |                                                      |       |

#### Chapter 22 SCC BISYNC Mode

| 22.1  | Features                                           |  |

|-------|----------------------------------------------------|--|

| 22.2  | SCC BISYNC Channel Frame Transmission              |  |

| 22.3  | SCC BISYNC Channel Frame Reception                 |  |

| 22.4  | SCC BISYNC Parameter RAM                           |  |

| 22.5  | SCC BISYNC Commands                                |  |

| 22.6  | SCC BISYNC Control Character Recognition           |  |

| 22.7  | BISYNC SYNC Register (BSYNC)                       |  |

| 22.8  | SCC BISYNC DLE Register (BDLE)                     |  |

| 22.9  | Sending and Receiving the Synchronization Sequence |  |

| 22.10 | Handling Errors in the SCC BISYNC                  |  |

| 22.11 | BISYNC Mode Register (PSMR)                        |  |

|       |                                                    |  |

| Paragraph<br>Number | Title                                                    | Page<br>Number |

|---------------------|----------------------------------------------------------|----------------|

| 22.12               | SCC BISYNC Receive BD (RxBD)                             |                |

| 22.13               | SCC BISYNC Transmit BD (TxBD)                            | 22-14          |

| 22.14               | BISYNC Event Register (SCCE)/BISYNC Mask Register (SCCM) |                |

| 22.15               | SCC Status Registers (SCCS)                              |                |

| 22.16               | Programming the SCC BISYNC Controller                    |                |

| 22.17               | SCC BISYNC Programming Example                           |                |

#### Chapter 23 SCC Transparent Mode

| 23.1       | Features                                                   | 23-1  |

|------------|------------------------------------------------------------|-------|

| 23.2       | SCC Transparent Channel Frame Transmission Process         |       |

| 23.3       | SCC Transparent Channel Frame Reception Process            | 23-2  |

| 23.4       | Achieving Synchronization in Transparent Mode              | 23-3  |

| 23.4.1     | Synchronization in NMSI Mode                               | 23-3  |

| 23.4.1.1   | In-Line Synchronization Pattern                            | 23-3  |

| 23.4.1.2   | External Synchronization Signals                           | 23-4  |

| 23.4.1.2.1 | External Synchronization Example                           | 23-4  |

| 23.4.1.3   | Transparent Mode without Explicit Synchronization          | 23-5  |

| 23.4.2     | Synchronization and the TSA                                | 23-5  |

| 23.4.2.1   | Inline Synchronization Pattern                             |       |

| 23.4.2.2   | Inherent Synchronization                                   | 23-6  |

| 23.4.3     | End of Frame Detection                                     |       |

| 23.5       | CRC Calculation in Transparent Mode                        |       |

| 23.6       | SCC Transparent Parameter RAM                              |       |

| 23.7       | SCC Transparent Commands                                   | 23-7  |

| 23.8       | Handling Errors in the Transparent Controller              |       |

| 23.9       | Transparent Mode and the PSMR                              |       |

| 23.10      | SCC Transparent Receive Buffer Descriptor (RxBD)           | 23-9  |

| 23.11      | SCC Transparent Transmit Buffer Descriptor (TxBD)          |       |

| 23.12      | SCC Transparent Event Register (SCCE)/Mask Register (SCCM) | 23-12 |

| 23.13      | SCC Status Register in Transparent Mode (SCCS)             | 23-13 |

| 23.14      | SCC2 Transparent Programming Example                       |       |

#### Chapter 24 SCC Ethernet Mode

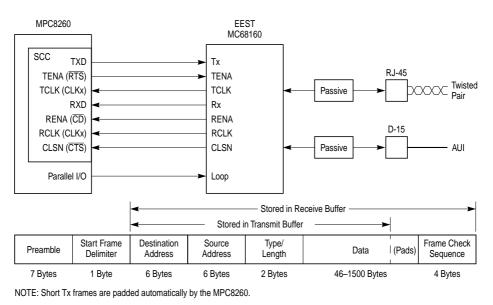

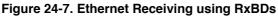

| 24.1 | Ethernet on the MPC8260                 | .24-2 |

|------|-----------------------------------------|-------|

| 24.2 | Features                                | .24-3 |

| 24.3 | Connecting the MPC8260 to Ethernet      | .24-4 |

| 24.4 | SCC Ethernet Channel Frame Transmission |       |

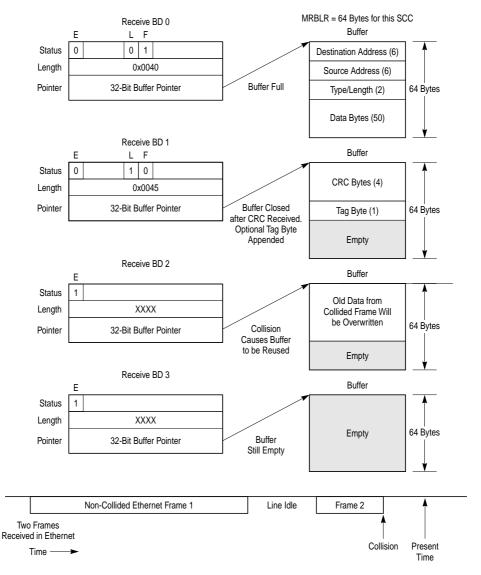

| 24.5 | SCC Ethernet Channel Frame Reception    | .24-6 |

| Paragraph<br>Number | Title                                                   | Page<br>Number |

|---------------------|---------------------------------------------------------|----------------|

| 24.6                | The Content-Addressable Memory (CAM) Interface          | 24-7           |

| 24.7                | SCC Ethernet Parameter RAM                              | 24-8           |

| 24.8                | Programming the Ethernet Controller                     | 24-10          |

| 24.9                | SCC Ethernet Commands                                   |                |

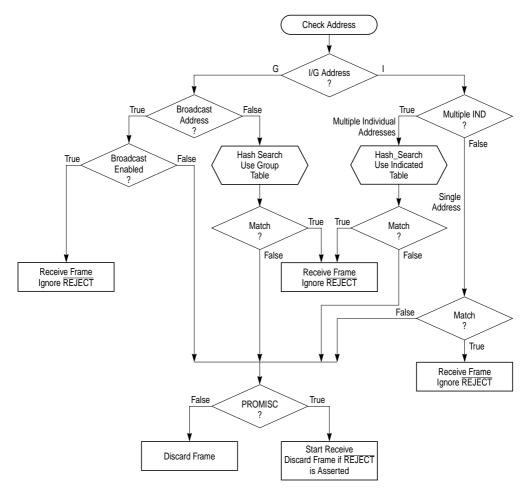

| 24.10               | SCC Ethernet Address Recognition                        | 24-11          |

| 24.11               | Hash Table Algorithm                                    |                |

| 24.12               | Interpacket Gap Time                                    |                |

| 24.13               | Handling Collisions                                     |                |

| 24.14               | Internal and External Loopback                          |                |

| 24.15               | Full-Duplex Ethernet Support                            |                |

| 24.16               | Handling Errors in the Ethernet Controller              |                |

| 24.17               | Ethernet Mode Register (PSMR)                           | 24-15          |

| 24.18               | SCC Ethernet Receive BD                                 |                |

| 24.19               | SCC Ethernet Transmit Buffer Descriptor                 | 24-19          |

| 24.20               | SCC Ethernet Event Register (SCCE)/Mask Register (SCCM) |                |

| 24.21               | SCC Ethernet Programming Example                        |                |

#### Chapter 25 SCC AppleTalk Mode

| 25.1   | Operating the LocalTalk Bus           |      |

|--------|---------------------------------------|------|

| 25.2   | Features                              |      |

| 25.3   | Connecting to AppleTalk               |      |

| 25.4   | Programming the SCC in AppleTalk Mode |      |

| 25.4.1 | Programming the GSMR                  |      |

| 25.4.2 | Programming the PSMR                  |      |

| 25.4.3 | Programming the TODR                  |      |

| 25.4.4 | SCC AppleTalk Programming Example     | 25-4 |

#### Chapter 26 Serial Management Controllers (SMCs)

| 26.1     | Features                                |  |

|----------|-----------------------------------------|--|

| 26.2     | Common SMC Settings and Configurations  |  |

| 26.2.1   | SMC Mode Registers (SMCMR1/SMCMR2)      |  |

| 26.2.2   | SMC Buffer Descriptor Operation         |  |

| 26.2.3   | SMC Parameter RAM                       |  |

| 26.2.3.1 | SMC Function Code Registers (RFCR/TFCR) |  |

| 26.2.4   | Disabling SMCs On-the-Fly               |  |

| 26.2.4.1 | SMC Transmitter Full Sequence           |  |

| 26.2.4.2 | SMC Transmitter Shortcut Sequence       |  |

| 26.2.4.3 | SMC Receiver Full Sequence.             |  |

| Paragraph<br>Number | Title                                                       | Page<br>Number |

|---------------------|-------------------------------------------------------------|----------------|

| 26.2.4.4            | SMC Receiver Shortcut Sequence                              |                |

| 26.2.4.5            | Switching Protocols                                         |                |

| 26.2.5              | Saving Power                                                |                |

| 26.2.6              | Handling Interrupts in the SMC                              |                |

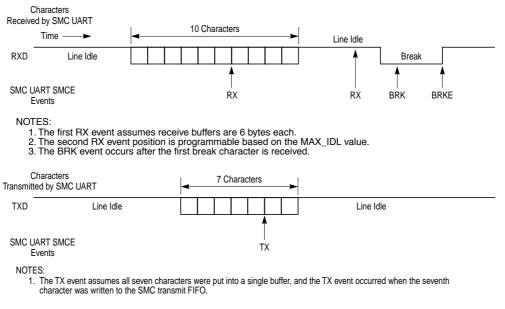

| 26.3                | SMC in UART Mode                                            |                |

| 26.3.1              | Features                                                    |                |

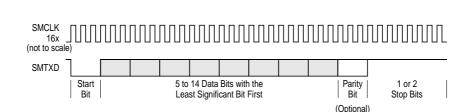

| 26.3.2              | SMC UART Channel Transmission Process                       |                |

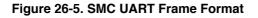

| 26.3.3              | SMC UART Channel Reception Process                          |                |

| 26.3.4              | Programming the SMC UART Controller                         |                |

| 26.3.5              | SMC UART Transmit and Receive Commands                      |                |

| 26.3.6              | Sending a Break                                             |                |

| 26.3.7              | Sending a Preamble                                          |                |

| 26.3.8              | Handling Errors in the SMC UART Controller                  |                |

| 26.3.9              | SMC UART RxBD                                               |                |

| 26.3.10             | SMC UART TxBD                                               |                |

| 26.3.11             | SMC UART Event Register (SMCE)/Mask Register (SMCM)         |                |

| 26.3.12             | SMC UART Controller Programming Example                     |                |

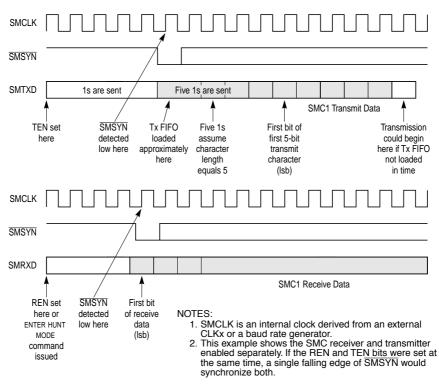

| 26.4                | SMC in Transparent Mode                                     |                |

| 26.4.1              | Features                                                    |                |

| 26.4.2              | SMC Transparent Channel Transmission Process                |                |

| 26.4.3              | SMC Transparent Channel Reception Process                   |                |

| 26.4.4              | Using SMSYN for Synchronization                             |                |

| 26.4.5              | Using the Time-Slot Assigner (TSA) for Synchronization      |                |

| 26.4.6              | SMC Transparent Commands                                    |                |

| 26.4.7              | Handling Errors in the SMC Transparent Controller           |                |

| 26.4.8              | SMC Transparent RxBD                                        |                |

| 26.4.9              | SMC Transparent TxBD                                        |                |

| 26.4.10             | SMC Transparent Event Register (SMCE)/Mask Register (SMCM). |                |

| 26.4.11             | SMC Transparent NMSI Programming Example                    |                |

| 26.5                | The SMC in GCI Mode                                         |                |

| 26.5.1              | SMC GCI Parameter RAM                                       |                |

| 26.5.2              | Handling the GCI Monitor Channel                            |                |

| 26.5.2.1            | SMC GCI Monitor Channel Transmission Process                |                |

| 26.5.2.2            | SMC GCI Monitor Channel Reception Process                   |                |

| 26.5.3              | Handling the GCI C/I Channel.                               |                |

| 26.5.3.1            | SMC GCI C/I Channel Transmission Process                    |                |

| 26.5.3.2            | SMC GCI C/I Channel Reception Process                       |                |

| 26.5.4              | SMC GCI Commands                                            |                |

| 26.5.5              | SMC GCI Monitor Channel RxBD                                |                |

| 26.5.6              | SMC GCI Monitor Channel TxBD                                |                |

| 26.5.7              | SMC GCI C/I Channel RxBD                                    |                |

| 26.5.8              | SMC GCI C/I Channel TxBD                                    |                |

| 26.5.9              | SMC GCI Event Register (SMCE)/Mask Register (SMCM)          |                |

| 20.0.0              |                                                             |                |

Paragraph Number

Title

Page Number

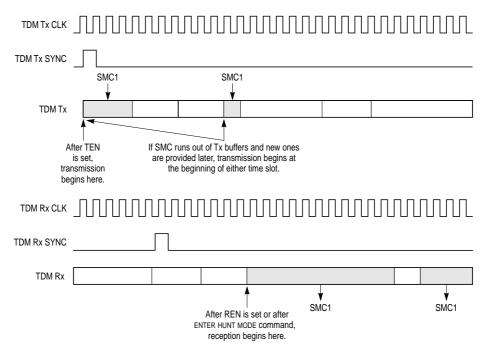

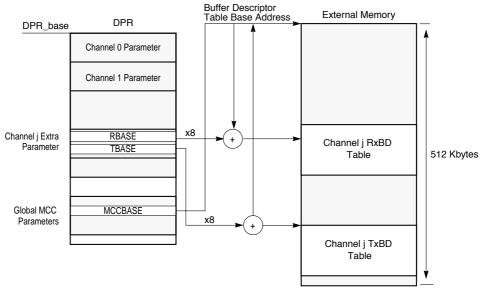

#### Chapter 27 Multi-Channel Controllers (MCCs)

| 27.1      | Features                                       | 27-1  |

|-----------|------------------------------------------------|-------|

| 27.2      | MCC Data Structure Organization                |       |

| 27.3      | Global MCC Parameters                          |       |

| 27.4      | Channel Extra Parameters                       |       |

| 27.5      | Super-Channel Table                            |       |

| 27.6      | Channel-Specific HDLC Parameters               |       |

| 27.6.1    | Internal Transmitter State (TSTATE)            | 27-9  |

| 27.6.2    | Interrupt Mask (INTMSK)                        | 27-9  |

| 27.6.3    | Channel Mode Register (CHAMR)                  | 27-10 |

| 27.6.4    | Internal Receiver State (RSTATE)               | 27-11 |

| 27.7      | Channel-Specific Transparent Parameters        | 27-12 |

| 27.7.1    | Channel Mode Register (CHAMR)-Transparent Mode | 27-13 |

| 27.8      | MCC Configuration Registers (MCCFx)            | 27-15 |

| 27.9      | MCC Commands                                   |       |

| 27.10     | MCC Exceptions                                 | 27-17 |

| 27.10.1   | MCC Event Register (MCCE)/Mask Register (MCCM) | 27-18 |

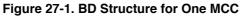

| 27.10.1.1 | Interrupt Table Entry                          | 27-19 |

| 27.11     | MCC Buffer Descriptors                         | 27-21 |

| 27.11.1   | Receive Buffer Descriptor (RxBD)               | 27-21 |

| 27.11.2   | Transmit Buffer Descriptor (TxBD)              | 27-23 |

| 27.12     | MCC Initialization and Start/Stop Sequence     | 27-24 |

| 27.12.1   | Single-Channel Initialization                  | 27-25 |

| 27.12.2   | Super Channel Initialization                   | 27-26 |

| 27.13     | MCC Latency and Performance                    | 27-26 |

#### Chapter 28 Fast Communications Controllers (FCCs)

| 28.1   | Overview                                      |  |

|--------|-----------------------------------------------|--|

| 28.2   | General FCC Mode Registers (GFMRx)            |  |

| 28.3   | FCC Protocol-Specific Mode Registers (FPSMRx) |  |

| 28.4   | FCC Data Synchronization Registers (FDSRx)    |  |

| 28.5   | FCC Transmit-on-Demand Registers (FTODRx)     |  |

| 28.6   | FCC Buffer Descriptors                        |  |

| 28.7   | FCC Parameter RAM                             |  |

| 28.7.1 | FCC Function Code Registers (FCRx)            |  |

| 28.8   | Interrupts from the FCCs                      |  |

| 28.8.1 | FCC Event Registers (FCCEx)                   |  |

| 28.8.2 | FCC Mask Registers (FCCMx)                    |  |

|        | -                                             |  |

| Paragraph<br>Number | Title                             | Page<br>Number |

|---------------------|-----------------------------------|----------------|

| 28.8.3              | FCC Status Registers (FCCSx)      |                |

| 28.9                | FCC Initialization                |                |

| 28.10               | FCC Interrupt Handling            |                |

| 28.11               | FCC Timing Control                |                |

| 28.12               | Disabling the FCCs On-the-Fly     |                |

| 28.12.1             | FCC Transmitter Full Sequence     |                |

| 28.12.2             | FCC Transmitter Shortcut Sequence |                |

| 28.12.3             | FCC Receiver Full Sequence        |                |

| 28.12.4             | FCC Receiver Shortcut Sequence    |                |

| 28.12.5             | Switching Protocols               |                |

| 28.13               | Saving Power                      |                |

#### Chapter 29 ATM Controller

| 29.1       | Features                                                   |       |

|------------|------------------------------------------------------------|-------|

| 29.2       | ATM Controller Overview                                    |       |

| 29.2.1     | Transmitter Overview                                       |       |

| 29.2.1.1   | AAL5 Transmitter Overview                                  |       |

| 29.2.1.2   | AAL1 Transmitter Overview                                  |       |

| 29.2.1.3   | AAL0 Transmitter Overview                                  |       |

| 29.2.1.4   | Transmit External Rate and Internal Rate Modes             |       |

| 29.2.2     | Receiver Overview                                          |       |

| 29.2.2.1   | AAL5 Receiver Overview                                     | 29-7  |

| 29.2.2.2   | AAL1 Receiver Overview                                     |       |

| 29.2.2.3   | AAL0 Receiver Overview                                     |       |

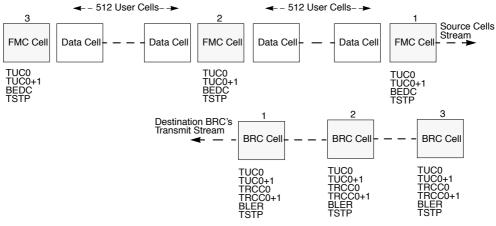

| 29.2.3     | Performance Monitoring                                     |       |

| 29.2.4     | ABR Flow Control                                           |       |

| 29.3       | ATM Pace Control (APC) Unit                                |       |

| 29.3.1     | APC Modes and ATM Service Types                            |       |

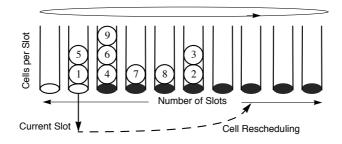

| 29.3.2     | APC Unit Scheduling Mechanism                              |       |

| 29.3.3     | Determining the Scheduling Table Size                      |       |

| 29.3.3.1   | Determining the Cells Per Slot (CPS) in a Scheduling Table |       |

| 29.3.3.2   | Determining the Number of Slots in a Scheduling Table      |       |

| 29.3.4     | Determining the Time-Slot Scheduling Rate of a Channel     |       |

| 29.3.5     | ATM Traffic Type                                           |       |

| 29.3.5.1   | Peak Cell Rate Traffic Type                                |       |

| 29.3.5.2   | Determining the PCR Traffic Type Parameters                |       |

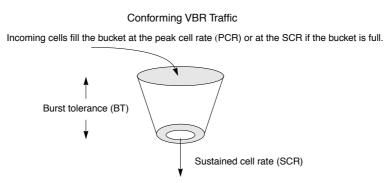

| 29.3.5.3   | Peak and Sustain Traffic Type (VBR)                        | 29-12 |

| 29.3.5.3.1 | Example for Using VBR Traffic Parameters                   |       |

| 29.3.5.3.2 | Handling the Cell Loss Priority (CLP)-VBR Type 1 and 2     |       |

| 29.3.5.4   | Peak and Minimum Cell Rate Traffic Type (UBR+)             |       |

| Paragraph<br>Number | Title                                            | Page<br>Number |

|---------------------|--------------------------------------------------|----------------|

| 29.3.6              | Determining the Priority of an ATM Channel       |                |

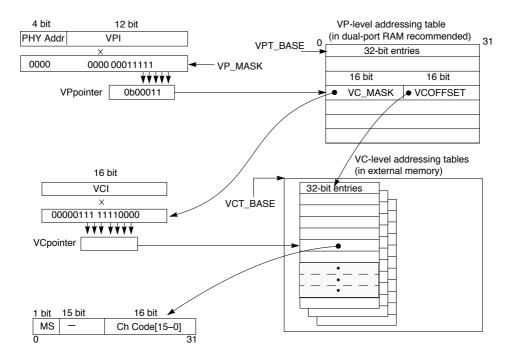

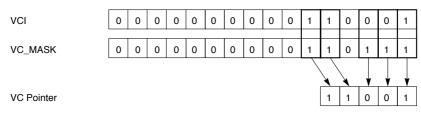

| 29.4                | VCI/VPI Address Lookup Mechanism                 |                |

| 29.4.1              | External CAM Lookup                              |                |

| 29.4.2              | Address Compression                              |                |

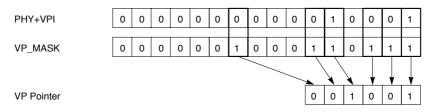

| 29.4.2.1            | VP-Level Address Compression Table (VPLT)        |                |

| 29.4.2.2            | VC-Level Address Compression Tables (VCLTs)      |                |

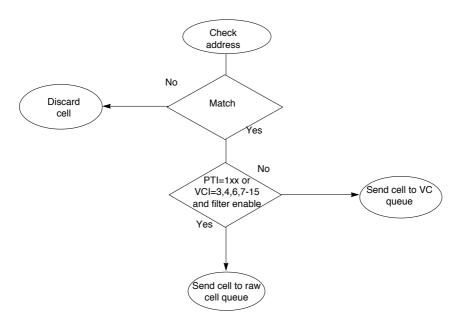

| 29.4.3              | Misinserted Cells                                |                |

| 29.4.4              | Receive Raw Cell Queue                           |                |

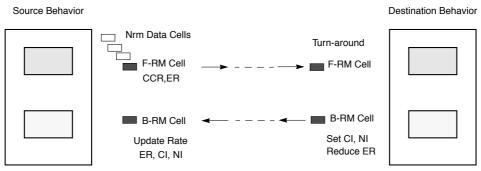

| 29.5                | Available Bit Rate (ABR) Flow Control            |                |

| 29.5.1              | The ABR Model                                    |                |

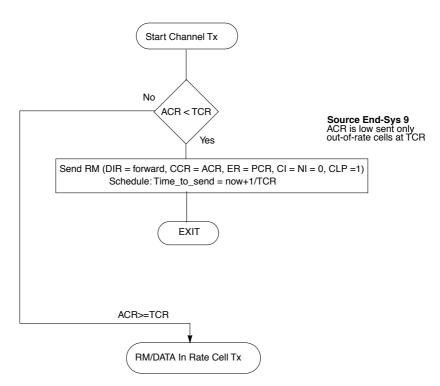

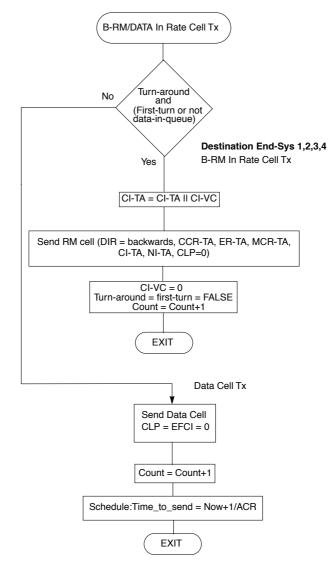

| 29.5.1.1            | ABR Flow Control Source End-System Behavior      |                |

| 29.5.1.2            | ABR Flow Control Destination End-System Behavior |                |

| 29.5.1.3            | ABR Flowcharts                                   |                |

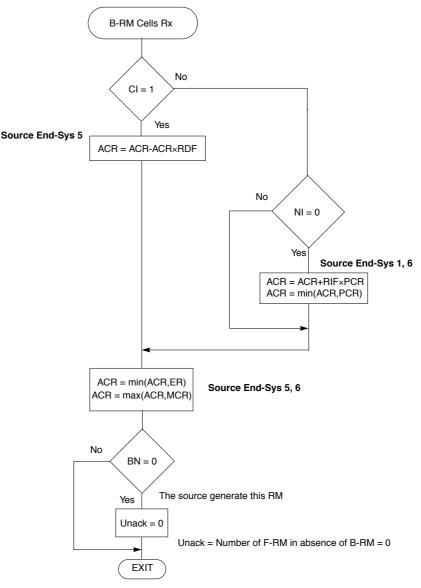

| 29.5.2              | RM Cell Structure                                |                |

| 29.5.2.1            | RM Cell Rate Representation                      |                |

| 29.5.3              | ABR Flow Control Setup                           |                |

| 29.6                | OAM Support                                      |                |

| 29.6.1              | ATM-Layer OAM Definitions                        |                |

| 29.6.2              | Virtual Path (F4) Flow Mechanism                 |                |

| 29.6.3              | Virtual Channel (F5) Flow Mechanism              |                |

| 29.6.4              | Receiving OAM F4 or F5 Cells                     |                |

| 29.6.5              | Transmitting OAM F4 or F5 Cells                  |                |

| 29.6.6              | Performance Monitoring                           |                |

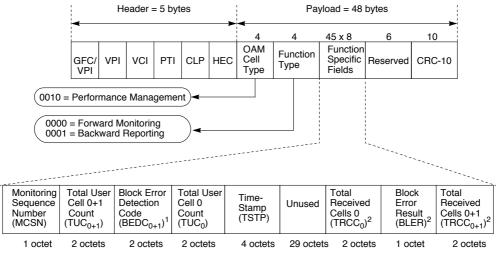

| 29.6.6.1            | Running a Performance Block Test                 |                |

| 29.6.6.2            | PM Block Monitoring                              |                |

| 29.6.6.3            | PM Block Generation                              |                |

| 29.6.6.4            | BRC Performance Calculations                     |                |

| 29.7                | User-Defined Cells (UDC)                         |                |

| 29.7.1              | UDC Extended Address Mode (UEAD)                 |                |

| 29.8                | ATM Layer Statistics                             |                |

| 29.9                | ATM-to-TDM Interworking                          |                |

| 29.9.1              | Automatic Data Forwarding                        |                |

| 29.9.2              | Using Interrupts in Automatic Data Forwarding    |                |