# ADVANCE INFORMATION Software Manual

## **LXT1001 Network Controller**

## LXT1001

## Software Reference Manual

### **General Description**

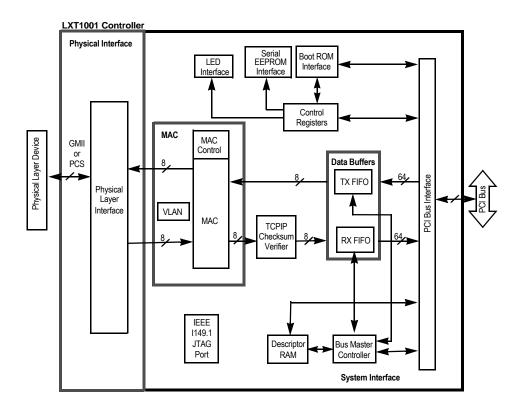

The LXT1001 10/100/1000 Mbps Ethernet controller provides the optimal combination of cost and system-level performance for network interface connections in server platforms and high-performance workstations.

The LXT1001 network controller is the first in a family of high-performance network accelerators by Level One Communications designed to meet the needs of high-speed network equipment. The LXT1001 incorporates a 10/100/1000 Mbps 802.3-compliant Media Access Controller (MAC) with extensive packet buffering and an optimized 64-bit PCI system interface. The LXT1001 MAC increases system performance by including high-level functions (e.g., VLAN filtering and IP packet processing) in the hardware. The PCI system interface uses the patent-pending Level One Communications Propulsion algorithms to achieve dramatic increases in system throughput.

#### **Features**

- Support 10, 100 and 1000 Mbps Ethernet

- Deep, independent, on-board receive (RX) and transmit (TX) FIFOs

- Peripheral Component Interconnect (PCI) v2.2 compliant interface supporting operation up to 33 MHz with a 64-bit wide data path

- Three data transfer methods: Programmed I/O (PIO);

Packet Descriptor List (PDL); and Propulsion™

Packet Descriptor Command (PDC)

- Full- and half-duplex operation, including carrier extension and packet bursting in half-duplex 1000 Mbps operation

- Symmetric and asymmetric flow control

- · Supports MII, GMII, and TBI

- 272-pin Plastic Ball Grid Array (PBGA) package

- Commercial Temp Range (0–70 °C)

### **ADDITIONAL LXT1001 FEATURES**

#### **Robust Drivers and Management**

Supporting software includes certified device drivers and end user diagnostics.

- Windows® NT 3.51, 4.0 and 5.0; Windows® 95

OSR2; Windows® 98; NetWare<sup>TM</sup> 3.12, 3.2, 4.2,

4.11 and 5.0; and Linux 2.0 and 2.2

- Support for the OnNow Initiative and PCI Power Management

- Wake-on-LAN  $^{TM}$  , Magic Packet  $^{TM}$  in PC1 Power Managed systems

- PCI PME Signal

- Required elements of the 802.3 MIB

#### **Optimized Bus Transfer Operation**

- High-Speed PCI Interface

- PCI 2.2 compliant

- Efficient PCI master operation

- 33MHz, 32-/64-bit operation

- 64-bit addressing

- Supports dual address cycles

- Supports three I/O methods

- · Programmed I/O

- Traditional scatter-gather "bus master" DMA

- Propulsion<sup>TM</sup> technology packet bursting across PCI bus increases the throughput for small packets

- Propulsion features

- Packet bursting across PCI bus

- Minimizes bus arbitrations

- Eliminates logical to physical address translation

- Scales to wider bus widths and faster clock rates

Minimizes interrupts by coalescing transfers across the PCI bus

#### **Expansion/Convenience Features**

- EEPROM Interface

- Single word read/writes or reads entire contents

- · Checksum after read, auto-detection

- Expansion ROM Interface

- Supports ROM, EPROM, and Flash memory

- Internally supports up to 4K expansion ROM

- Up to one megabyte can be supported using external logic

- Supports up to four individually programmable LEDs

- IEEE 1149.1a-1993 (JTAG)-compliant boundary scan

#### **Technology Features**

- · State machine design

- 0.35 micron process

- Plastic Ball Grid Array (PBGA) package

- 3.3-volt/5-volt-tolerant I/Os

- Targeted power consumption of less than 1.5W (typical)

## Host Offloading and Policy-Based Behavior

- IPv4 checksum calculation on chip

- IP, TCP and UDP checksums supported

- Packet filtering based on checksum errors

- 802.3ac and VLAN tag support

- Programmable 16-entry table; Filtering based on recognized VLANs; VLAN tag stripping on receive; Global and/or per packet VLAN tag insertion on transmit

## **TABLE OF CONTENTS**

| SECTION 1 TYPES OF REGISTERS               | 7  | Interrupt Handler                         | 40       |

|--------------------------------------------|----|-------------------------------------------|----------|

| SECTION 2 THEORY OF OPERATIONS             | 9  | VLAN Support                              |          |

| Input/Output Methods                       |    | TCP/IP Checksum Support                   | 43       |

| Programmed Input/Output                    |    | EEPROM Support                            |          |

| Packet Descriptor List                     |    | Expansion ROM Support                     | 44       |

| Packet Propulsion Method (Packet           | /  | Magic Packet Wake Up PCI Power Management | 44<br>15 |

| Descriptor Command)                        | 12 | SECTION 3 PCI CONFIGURATION               | 4.       |

| Organization                               |    |                                           | 47       |

| Initialization                             | 17 | REGISTERS                                 | 41       |

| Reset                                      |    | SECTION 4 COMMAND AND STATUS              |          |

| Physical Layer Configuration and Status    |    | REGISTERS                                 |          |

| PDC Buffer Allocation                      |    | CSR 00 Mode Register – 1                  |          |

| PDL Buffer Allocation                      |    | CSR 01 Mode Register – 2                  | 54       |

| System Initialization Event Sequence       |    | CSR 02 Transmit PDC Buffer Address        |          |

| Initialization Algorithm                   |    | Table Index                               | 56       |

| Transmit Packet Processing                 |    | CSR 03 Product Identification Register    | 57       |

| Transmit Packet Padding                    |    | CSR 04 Transmit PDC Buffer Address        |          |

| VLAN Tag Header Insertion                  |    | LSD                                       | 57       |

| CRC Generation                             |    | CSR 05 Transmit PDC Buffer Address        |          |

| Transmit Completion Status                 |    | MSD                                       | 58       |

| Transmit Statistics                        |    | CSR 06 Receive PDC Buffer Address         |          |

| Simultaneous Use of PDL, PDC, and PIO      | 23 | Table Index                               | 58       |

| I/O Methods                                | 23 | CSR 07 Reserved                           |          |

| Programmed Input/Output Method of          | 23 | CSR08 Receive PDC Buffer Address          |          |

| Transmission                               | 24 | LSD                                       | 60       |

| Packet Descriptor List Method of           | 24 | CSR 09 Receive PDC Buffer Address         |          |

| Transmission                               | 26 | MSD                                       | 60       |

| Packet Propulsion Mode Method of           | 20 | CSR 10 EEPROM Register                    |          |

| Transmission                               | 28 | CSR 11 Chip Status Register               |          |

| Receive Packet Processing                  |    | CSR12 Transmit PDL Address Register       |          |

| Packet Reception Filters                   | 31 | LSD                                       | 66       |

| Packet Receive Status                      |    | CSR 13 Transmit PDL Address Register      | 00       |

| Receive Statistics                         |    | MSD                                       | 68       |

| Large Packet Reception                     |    | CSR 14 Receive PDL Address Register       | 00       |

| Simultaneous Use of PDL, PDC, and PIO      | 31 | LSD                                       | 65       |

| I/O Methods                                | 32 | CSR 15 Receive PDL Address Register       | 00       |

| Programmed Input/Output (PIO) Method of    | 34 | MSD                                       | 73       |

| Reception                                  | 32 | CSR16 Transmit PDC Register               |          |

| Packet Descriptor List Method of Reception |    | CSR 17 Receive PDC Register               |          |

| Packet Propulsion Mode Method of           |    | CSR 18 Interrupt Period Register          | / (      |

| Reception                                  | 36 |                                           | 70       |

| Packet Propulsion Mode Receive             |    | ReservedCSR 19 TX FIFO Packet Count       | /5       |

| Algorithm                                  | 36 |                                           | 70       |

| Interrupt Processing                       |    | Register                                  | /5       |

| Event Status Register                      | 39 | CSR 20 TX FIFO Low Watermark              | 0.0      |

| Interrupt Mask Register                    | 39 | Register                                  | 80       |

| CSR 21 TX FIFO DWORDs Free              | CSR 50 Reserved                        | 105 |

|-----------------------------------------|----------------------------------------|-----|

| Register 80                             | CSR 51 Command Status Register         | 106 |

| CSR 22 TX FIFO Write Register 81        | CSR 52 Flow Control Watermark          |     |

| CSR 23 Reserved 82                      | Register                               | 107 |

| CSR 24 RX FIFO Read Register 82         | CSR 53 Reserved                        |     |

| CSR 25 Reserved                         | CSR 54 Reserved                        |     |

| CSR 26 RX FIFO DWORD Count              | CSR 55 Reserved                        | 108 |

| Register 85                             | CSR 56 Reserved                        |     |

| CSR 27 RX FIFO High Watermark           | CSR 57 Reserved                        | 109 |

| Register85                              | CSR 58 Timer 0 Count Register          | 110 |

| CSR 28 RX FIFO Packet Count Register 86 | CSR 59 Timer 0 Interrupt Trigger       |     |

| CSR 29 Command Register 86              | Register                               | 110 |

| CSR 30 Interrupt Mask Register 88       | CSR 60 Timer 1 Count Register          | 111 |

| CSR 31 Reserved                         | CSR 61 Timer 1 Interrupt Trigger       |     |

| CSR 32 Event Status Register90          | Register                               | 111 |

| CSR 33 Reserved                         | CSR 62 Debug Command Register          | 112 |

| CSR 34 Multicast Hash Table             | CSR 63 Debug Data Register             | 112 |

| Register LSD93                          | PCS Interface Registers                |     |

| CSR 35 Multicast Hash Table             | Register 0 Control Register            |     |

| Register MSD94                          | Register 1 Status Register             |     |

| CSR 36 LED 0 Configuration Register 94  | Register 2 & 3 PHY Identifier Register | 116 |

| CSR 37 LED 1 Configuration Register 95  | Register 4 Auto-Negotiation            |     |

| CSR 38 LED 2 Configuration Register 96  | Advertisement Register                 | 116 |

| CSR 39 LED 3 Configuration Register 96  | Register 5 Auto-Negotiation Link       |     |

| CSR 40 Reserved                         | Partner Base Page Ability Register     | 117 |

| CSR 41 EEPROM Data Register97           | Register 6 Auto-Negotiation            |     |

| CSR 42 LAN Physical Address             | Expansion Register                     | 118 |

| Register LSD97                          | Register 7 Auto-Negotiation Next       |     |

| CSR 43 LAN Physical Address             | Page Transmit Register                 | 119 |

| Register MSW98                          | Register 8 Auto-Negotiation Link       |     |

| CSR 44 G/MII PHY Access Register 99     | Partner Received Next Page Register    | 120 |

| CSR 45 G/MII Mode Register 100          | Register 15 Extended Status Register   | 121 |

| CSR 46 Statistic Index Register 101     | Vendor Specific Registers              | 122 |

| CSR 47 Statistic Value Register 103     | Register 16 Level One Communications   |     |

| CSR 48 VLAN Tag Control                 | Features Register                      |     |

| Information Table 104                   | SECTION 5 EEPROM MAP                   | 123 |

| CSD 40 Pagaryad                         | SECTION & GLOSSADY                     | 125 |

## **LIST OF FIGURES**

| Figure 2-1: | PIO Data Transfer Process9        | Figure 4-4: | PDC Transmit Header and |     |

|-------------|-----------------------------------|-------------|-------------------------|-----|

| Figure 2-2: | Transmit Packet Descriptor List10 |             | Data Format             | 75  |

| Figure 2-3: | PDL Data Transfer Process11       | Figure 4-5: | PDC Receive Header and  |     |

| Figure 2-4: | PDC Data Transfer Process15       |             | Data Format             | 77  |

| Figure 2-5: | VLAN Header Format43              | Figure 4-6: | PDC Null Header Format  | 78  |

| Figure 3-1: | PCI Configuration Space           | Figure 4-7: | PIO Transmit Header and |     |

|             | Register Map47                    |             | Data Format             | 81  |

| Figure 4-1: | PDL Transmit Header Format67      | Figure 4-8: | PIO Receive Header and  |     |

| Figure 4-2: | PDL Pre-Receive Header Format70   |             | Data Format             | 83  |

| Figure 4-3: | PDL Post-Receive Header Format71  | Figure 5-1: | EEPROM Map              | 123 |

|             |                                   |             |                         |     |

## **SECTION 1 TYPES OF REGISTERS**

Several types of registers are used in the LXT1001. They are as follows:

- · Control and Status Registers.

- Control and Status Registers (CSRs) are accessible by HOST software. CSRs are used to control the operational behavior of the LXT1001 and ascertain its status. In particular, CSRs can be read/write, read only, write only, or a combination of all three. The read/write attribute of a particular bit or sequence of bits in a CSR is individually set. That is to say, a CSR can be entirely dedicated to one function (as is the case with the *Transmit PDL Address Register*), or can be subdivided into one or more bit fields (like *Mode Register* 1), each having its own read/write behavior.

- Frequently accessed bit fields in CSRs are implemented as set/reset registers. This type of register is subdivided into one or more mask bits and one or more set/reset control bits. The mask bits determine whether a particular bit will be affected by a given write operation. For example, a mask value of 1001b will allow a write to the least significant bit (LSB) and most significant bit (MSB) of a 4-bit field while preventing writes to the middle bits. If the control bit is set to 1, then the MSB and LSB will have 1s written to them. If the control bit is set to 0, then the MSB and LSB will have 0s written to them. Again, in both cases the contents of the middle bits remain unchanged. When set/reset registers are read, the set/reset bits are ignored (actually, they are read as 0s) and those bit fields that have an R/W attribute will return their current value.  $Mode\ Register - 1$  is an example of a set/reset CSR.

- Some CSR bit fields are self-clearing. When set by HOST software, self-clearing bit fields remain set until some activity completes, at which point the bit field is automatically reset by the LXT1001. Self-clearing bits can be polled by HOST software to determine when the activity has completed. The SWRE bit in *Mode Register 1* is an example of an auto-reset bit (field).

- Some CSR registers are automatically cleared when read. Typically, this type of behavior is used in counter registers. Once the count is retrieved, the register resets and counting begins again at some predetermined value, usually 0. The Event

- Status Register is an example of a clear when read register.

- CSRs are either 32 or 64 bits wide and can be accessed using either I/O or memory cycles.

- The 64-bit registers are accessed 32 bits at a time. However, 64-bit registers that affect an action when read or written must be accessed most significant DWORD (MSD) first. For example, to pass the address of a transmit PDL to the LXT1001, the MSD is written first, followed by the least significant DWORD (LSD). When the LXT1001 detects the write to the LSD of the *Transmit PDL Address Register*, it will assume that all 64 bits have been written and that the operation can begin.

- In cases where extensive bit manipulation of CSRs is expected, the most heavily used bits are kept in the low order 16 bits of the register. This is done to accommodate the byte- and word-oriented operations of x86 microprocessors.

- The CSRs are defined in Section 4.

- PCI Configuration Space Registers.

- The LXT1001 configuration is achieved by partially using PCI configuration space registers and partially using CSRs. Configuration aspects pertaining to system resources, such as interrupts and address space, are handled in the standard manner using PCI configuration registers.

Configuration of the operational characteristics of the LXT1001 (e.g., wire speed, reception of multicast frames, etc.) is done by programming specific values into CSRs.

- The PCI configuration registers adhere to the PCI v2.2 Specification and the PCI Power Management Specification. See Section 4 for a map of the configuration registers.

- All of the PCI configuration registers and the CSR registers can be read or written from the PCI bus, EEPROM, or internal blocks.

- As previously noted, the device registers that are visible on the PCI bus can either be I/O mapped or memory mapped in PCI address space.

- The registers are all aligned on DWORD boundaries.

- The registers support 8-, 16-, 32-, and 64-bit accesses. Note that at this time, the PCI bus only

supports 32-bit I/O. All 64-bit accesses are for memory cycles only. Although 64-bit I/O is not currently supported, it is expected that it will be defined in the standard and supported by CPUs within the lifetime of the LXT1001.

• The LXT1001 CSRs are organized to accommodate high-performance drivers. The registers have been organized to minimize the bit manipulations required for mainstream packet processing.

### **SECTION 2 THEORY OF OPERATIONS**

## Input/Output Methods

Three I/O methods are defined for the LXT1001: programmed input/output (PIO), packet descriptor list (PDL), and packet Propulsion (PDC) I/O method. Of these three methods, PIO and PDL are extensively used in conventional ethernet adapters and are described briefly below. The third technique, packet Propulsion I/O method, is Level One Technologies' unique and proprietary data transfer method designed to highly optimize packet processing for increased I/O bus utilization and data throughput.

## **Programmed Input/Output**

The PIO method implemented in the LXT1001 is a traditional I/O method where the CPU moves data into and

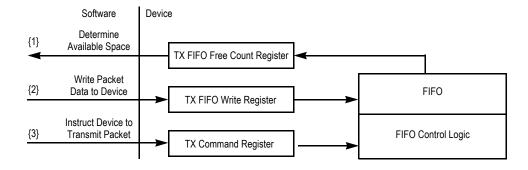

out of the device. CPU read and write operations (IN and OUT instructions in the x86 instruction set) are performed to device registers to either place data to be transmitted into the transmit data buffer (TX FIFO) or to extract data from the receive data buffer (RX FIFO). **Figure 2-1** depicts the process as it is applied when transmitting a packet. Step (1) determines whether the packet to be transmitted fits into the TX FIFO (in the diagram, it is assumed that the packet fits). Step (2) transfers the data to the device. The CPU performs this task by repeatedly writing DWORDs of packet data to the TX FIFO Write Register until all packet data is exhausted. Step (3) informs the device that a complete packet has been placed into the TX FIFO. Upon receiving this indication, the device will initiate transmission of the packet at the next available opportunity.

Figure 2-1: PIO Data Transfer Process

## **Packet Descriptor List**

The PDL technique is also commonly referred to as scatter-gather bus master. The PDL is a data structure that is comprised of a header followed by a number of packet fragment descriptors. The header specifies the total length of the packet (the sum of the lengths of the fragments), the

number of fragments, and option flags indicating any special processing requirements for the packet. The fragment descriptors specify the physical memory addresses of the buffer fragments and their individual lengths. The data structure is arranged as follows (bit 0 is the LSB):

Figure 2-2: Transmit Packet Descriptor List

| 31                                   | 30 | 2                                         | 20 16            | 15     | 0<br>0           |

|--------------------------------------|----|-------------------------------------------|------------------|--------|------------------|

| D<br>M<br>D<br>N<br>I<br>N<br>R<br>Q |    | T<br>X<br>O<br>P<br>T<br>I<br>O<br>N<br>S | F<br>G<br>C<br>N |        | P<br>K<br>L<br>E |

|                                      |    |                                           |                  | SRVD   |                  |

|                                      |    |                                           |                  | LSD 0  |                  |

|                                      |    |                                           | FGAD             | MSD 0  |                  |

|                                      |    | RESRVD                                    |                  |        | SLE 0            |

|                                      |    |                                           |                  | SRVD   |                  |

|                                      |    |                                           |                  | LSD 1  |                  |

|                                      |    |                                           | FGAD             | MSD 1  |                  |

|                                      |    | RESRVD                                    |                  |        | SLE 1            |

|                                      |    |                                           | RES              | SRVD   |                  |

|                                      |    |                                           |                  | •      | ·                |

|                                      |    |                                           |                  | •      |                  |

|                                      |    |                                           |                  | •      |                  |

|                                      |    |                                           | FGAD             | LSD 30 |                  |

|                                      |    |                                           | FGAD             | MSD 30 |                  |

|                                      |    | RESRVD                                    |                  | FG     | LE 30            |

|                                      |    |                                           | RES              | SRVD   |                  |

For clarity, the field names are briefly defined below:

**PKLE** — *Packet Length*. The sum of the lengths of the individual fragments.

**FGCN** — *Fragment Count*. The count of fragments defined within the PDL.

**TXOPTIONS** — Per Packet Transmission Options.

**DMDNINRQ** — Request for Interrupt Upon Completion of the Packet Transfer to the LXT1001.

**FGAD LSD n** — Fragment n Address, Least Significant DWORD.

**FGAD MSD n** — Fragment n Address, Most Significant DWORD.

**FGLE n** — *Fragment n Length.*

Details pertaining to this data structure are presented in the section describing the CSR12 Transmit PDL Address Register LSD on page 66. The PDL for receive is virtually identical. It is described in detail in CSR 14 Receive PDL Address Register LSD on page 68 and CSR 15 Receive PDL Address Register MSD on page 73.

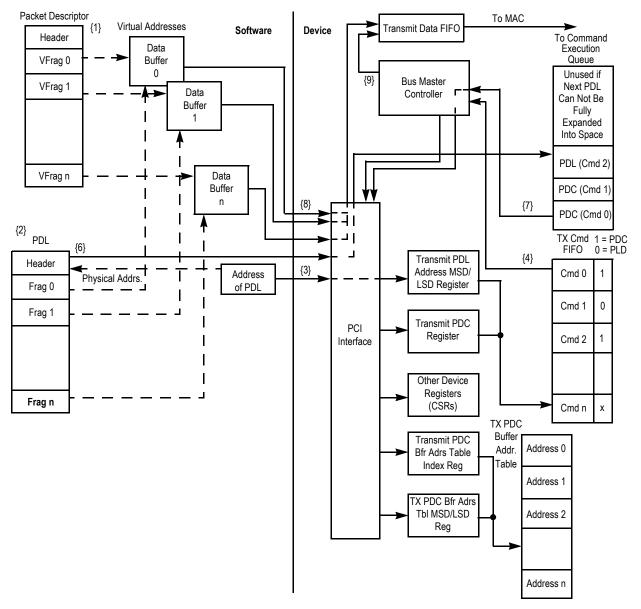

**Figure 2-3** depicts the interaction between the LXT1001 and its supporting system software when performing PDL DMA transfers. Although the diagram is presented from the vantage point of packet transmission, packet reception behaves in almost the same fashion. The differences are highlighted at the end of the sub-section.

Figure 2-3: PDL Data Transfer Process

In **Figure 2-3**, the sequence for packet transmission is as follows:

- An indication is received by the LXT1001 system software that a packet is to be transmitted. The indication is accompanied by some form of packet descriptor data structure usually containing multiple packet buffer fragments that are to be sent in the sequence that they are found in the descriptor.

- 2. The addresses of the packet fragments found in

the packet descriptor can be virtual or physical addresses. It is typical for them to be the virtual addresses of buffers constructed by a protocol stack. In this case, virtual addresses must be converted to physical addresses. This operation usually involves a call into the HOST operating system. Once the physical addresses for the packet are known, they are stored in the fragment address fields of the PDL's fragment descriptors.

3. After completely formatting the PDL (i.e., once it fully describes the packet to be transmitted), it can

be passed to the LXT1001 for processing. To do this, the starting physical address of the PDL in HOST memory is written to the *Transmit PDL Address MSD Register/LSD Register*. This action has the effect of placing the PDL's address into the transmit command FIFO.

- 4. When one or more commands are present in the transmit command FIFO, the bus master LXT1001 (BMC) examines the FIFO and extracts the first available command. In our example, the queue is assumed to be empty prior to the transmit request, and thus the PDL is acted upon at the first available opportunity.

- 5. When the BMC looks at the command FIFO, it determines that the command is a PDL. Consequently, the BMC issues a request to the PCI block for the transfer of the PDL data structure from HOST memory to the Command Execution Queue (i.e., the header field and the fragment fields).

- The PCI block responds to the request by effecting the necessary cycles on the bus to transfer the PDL into the Command Execution Queue.

- 7. Once the PDL is at the front of the Command Execution Queue, the BMC begins to "execute" it. It does so by interpreting the header, setting up its counters, pointers, etc., and then issuing commands to the PCI block to effect data transfers from HOST memory to the transmit data FIFO. For every fragment in the PDL, the BMC issues one data transfer command to the PCI block.

- 8. The PCI block transfers each packet fragment, one at a time to the transmit data FIFO.

- Once the packet is completely transferred to the transmit data FIFO, the BMC signals the data FIFO that a complete packet has been transferred. The FIFO control logic then updates its pointers and signals the MAC that a packet is ready for transmission.

The process for receiving a frame differs from the process described above in two respects:

- 1. The direction of the data flow is reversed.

- 2. The receive process is driven by the availability of incoming data and the availability of PDLs in the

receive command FIFO. In other words, if a packet arrives and there is no PDL or PDC in the receive command FIFO, then the packet will remain in the receive data FIFO until a PDL or PDC is placed into the receive command FIFO.

## Packet Propulsion Method (Packet Descriptor Command)

The PDC method for moving data is a specialization of the traditional PDL technique. As previously noted, the principle notion of PDL is that a bus master device is instructed to obtain a command block from HOST system memory. At a minimum, the command block contains a list of the physical addresses of the packet fragment buffers in HOST memory that are to be copied to the device, the count of packet buffer fragments, and the overall length of the data contained in the fragments (the sum of the lengths of the individual fragments).

The device parses the command block, extracting the address of each block of memory (fragment) to process, and effects a transfer of the said fragment from HOST memory to the device. The device repeats this process for each fragment listed in the PDL until all of the data described by the command is copied to the LXT1001 for transmission (the direction of the data flow is reversed for receive).

Contemplating the nature of the most important modern operating systems, several key points become apparent:

- They support and practically require virtual memory.

- Devices that initiate data movement transactions across peripheral interconnect busses cannot use virtual memory addresses to affect the transfers.

- In terms of performance, the conversion of virtual addresses to physical addresses is an expensive one.

These points are significant primarily because of the sequence of events they impose on bus master devices. Again considering the traditional PDL technique, when data is passed to a bus master device, the corresponding device driver must first perform a virtual to physical address conversion for each of the buffer fragments in the data transfer operation. Moreover, a typical buffer passed to the device is broken up into several buffer fragments. That is, the data to be transferred to the device is segmented into several pieces (typically three or four pieces). These facts result in a situation whereby the cost of converting a virtual address to a physical one can be repeated several times for each block of data that is to be transferred to the device. Given that the conversions are expensive, it is desirable to avoid them.

One method for avoiding the virtual-to-physical address translations is for the device driver to allocate blocks of locked memory during device initialization. The address conversion for these blocks can be performed once — at the point where the memory is allocated — and the physical address can be stored away (e.g., in a queue). Each time that a request to transfer data to the device is received from the upper layers, the device driver could very quickly remove the next available memory block from the queue, copy the data provided by the upper layer into the memory block, format a PDL, and then pass the PDL to the LXT1001. This method has the following advantages:

- Virtual to physical address translation is avoided.

- The formatting of the PDL is simplified.

- The amount of data to be transferred to the LXT1001 in the PDL itself is reduced.

This method for processing DMAs is frequently referred to as "double copy" or "double buffer" DMA. Several observations can be made regarding this technique:

- The fragment count is always 1.

- The length value in the PDL header is the same as the length value of the first fragment.

- The physical address placed into the first fragment address field in the PDL is one of *n* possible physical addresses of pre-allocated locked buffers. Usually, *n* is 16, 32, 64, or some other suitably small integer (i.e., typically *n* <= 128, although it appears that future

drivers may begin using values for n that are more in the range of  $128 \le n \le 1024$ ).

Once it is clear that some of the fields in the PDL will always have either the same value, or one value out of a small set of values, an expedited form of double buffering becomes possible. This expedited double buffer technique is called Propulsion technology, or PDC.

The principal ideas behind Propulsion technology are as follows:

- No command block (i.e., PDL) is formatted in HOST memory. Data transfer commands are communicated to the LXT1001 by passing a packet descriptor command. A PDC is a 32-bit value, subdivided into fields, that completely describes the data transfer operation. A PDC fits entirely within a device register and can be constructed entirely within a CPU register.

- Only one fragment (data buffer) per data transfer operation is communicated to the LXT1001 using a PDC (i.e., one buffer completely contains all of the data to be transferred to/from the LXT1001).

- The address of the data buffer is passed to the LXT1001 using a small (8-bit) ordinal value that indexes a table maintained on the LXT1001. The table has the complete set of physical addresses of buffers allocated by the DRIVER for data transfer purposes.

- The length of the buffer to be copied to/from LXT1001 is contained within the PDC command.

The actual format of a PDC command is as follows:

| 3 | 3 | 2 | 2 | 2 | 2 | 2 | 2 | 2 | 2 | 2 | 2 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 |

|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|

| 1 | 0 | 9 | 8 | 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 | 9 | 8 | 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 | 9 | 8 | 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 |

|   |   |   | R |   |   |   | X |   |   |   | F | 3 |   |   |   |   |   |   |   |   |   |   | ] | 3 |   |   |   |   |   |   |   |

|   |   |   | E |   |   |   | F |   |   |   | F | 7 |   |   |   |   |   |   |   |   |   |   | ] | F |   |   |   |   |   |   |   |

|   |   |   | S |   |   |   | D |   |   |   | ] | [ |   |   |   |   |   |   |   |   |   |   | ] | Ĺ |   |   |   |   |   |   |   |

|   |   |   | R |   |   |   | N |   |   |   | Ι | ) |   |   |   |   |   |   |   |   |   |   | ] | Ε |   |   |   |   |   |   |   |

|   |   |   | V |   |   |   | I |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |

|   |   |   | D |   |   |   | N |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |

|   |   |   |   |   |   |   | R |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |

|   |   |   |   |   |   |   | Q |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |

Upon closer inspection, one other optimization can be realized with the PDC technique. There is no restriction inherent to the PDC technique that prevents multiple packets from being copied by the HOST (or the LXT1001, depending on direction) into the pre-allocated data transfer buffers. In fact, if the data format used for the pre-allocated buffers parallels the data formats used internally by the LXT1001, then multiple packets can be easily formatted

into the PDC buffers and subsequently transferred to the LXT1001 with one I/O operation by the HOST (PDC command transfer to the LXT1001) and one burst transfer of data by the LXT1001.

Thus, the Propulsion technique is efficient in its use of bus bandwidth by minimizing the per-buffer overhead associated with the transfer of data to/from the LXT1001. Note that the per-buffer overhead includes the number of

interactions between HOST software and the LXT1001 (e.g., interrupts (especially on receive since multiple packets can be delivered into a single PDC and only one interrupt is generated to signal their arrival)) command block exchanges, and PIO operations to the device.

Although the PDC technique is very efficient in its use of bus bandwidth, this efficiency does not come without a price. The single most significant drawback of the PDC method is that it requires that the processor move data from application buffers into data transfer buffers — in other words, increased CPU utilization. At first glance, this double copy would seem an insurmountable obstacle to the emergence of PDC as the preferred data transfer technique. However, when one considers that on average many tens, if not hundreds, of CPU clocks are expended in performing virtual-to-physical address translations, and that often times, many such translations are performed per buffer transferred to the LXT1001, it becomes evident that a large amount of data can be moved by the CPU in the same

amount of time taken for an address translation. Certainly for small data transfers (and virtually half of all data transfers are small), the technique is useful since many tens, if not hundreds, of bytes can be moved in the time it takes to make just one virtual-to-physical address translation. Moreover, as CPUs move to 64-bit and larger word sizes, the efficacy of this technique increases.

Another significant point is that the concern over CPU utilization is not paramount in all systems. Especially in systems where large amounts of data are moved about (e.g., bus utilization is high) and the CPU has nothing else to do, then favoring bus utilization at the expense of CPU utilization can be a desirable trade-off to make. This argument can be extended to multiprocessor machines where CPU bandwidth outpaces bus bandwidth by a large margin. Here, too, expending CPU utilization to gain bus utilization may be a worthwhile trade-off.

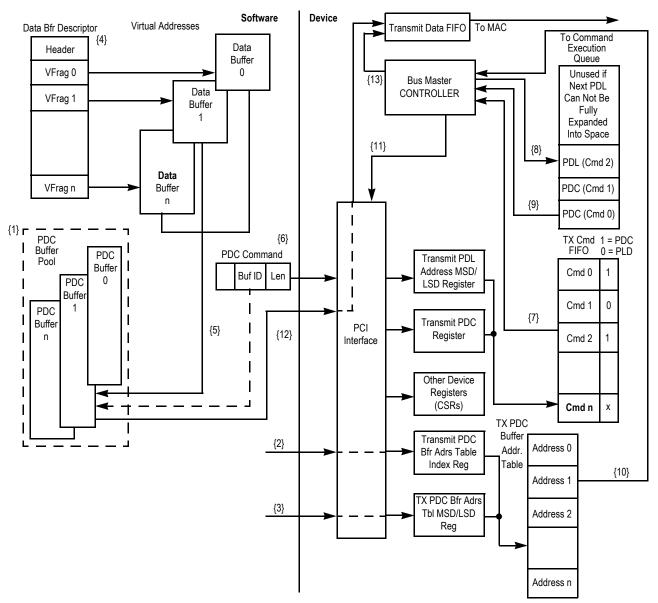

Figure 2-4 depicts the process of data transfer using PDCs.

Figure 2-4: PDC Data Transfer Process

The sequence for packet transmission when using PDCs is actually broken into two phases. The first phase happens once during device/driver initialization. It consists of steps 1, 2, and 3, as follows:

- 1. A pool of locked buffers is allocated from the system. Each buffer is made large enough to accommodate one or more full-size packets. If the individual buffers are made larger than the HOST system's page size (for virtual memory systems), the buffers must be contiguous (i.e., in adjacent

- pages with the lowest physical address residing in the lowest numbered page).

- 2. The *Transmit PDC Buffer Address Table Index Register* is pointed to the number 0 Buffer Address Table slot.

- 3. The addresses of the buffers in the pool are written to the table. Several important points can be mentioned here:

- a. The Transmit PDC Buffer Address Table does not need to be fully utilized. For example, if only two transmit PDC buffers are desired, then only two Transmit PDC Buffer Address Table entries need be used.

- b. Addresses in the table do not need to be in adjacent slots.

- Addresses in the table do not need to be in any particular order.

- d. The Transmit PDC Buffer Address Table Index Register auto-increments with each write to the Transmit PDC Buffer Address LSD Register.

This facilitates the writing of strings of buffer addresses to the device. However, the index register can be written prior to every write to the address MSD/LSD registers, thus allowing random write access to the table (both the address and index registers are write only).

The second phase is comprised of steps 4 through 13. These steps happen each time one or more packets are transmitted using a PDC buffer:

- 4. An indication is received by the LXT1001 system software that one or more packets are to be transmitted. The indication is accompanied by some form of packet descriptor data structure usually containing multiple packet buffer fragments (possibly describing multiple packets) that are to be sent in the sequence that they are found in the descriptor.

- 5. The addresses of the packet fragments found in the packet descriptor can be virtual or physical addresses. It is typical for them to be the virtual addresses of packet buffer fragments constructed by a protocol stack. The driver software responds by allocating (dequeing) a PDC buffer from the PDC buffer pool and block copying the packet(s) into successive locations within the PDC buffer. Note that in the case where multiple packets are transferred using a single PDC buffer, "fence posts" are inserted between the packets. Details pertaining to the fence posts are provided in the section describing the *Transmit PDC LSD Register*.

- 6. After copying all of the packet data to a PDC buffer, a PDC is formatted and passed to the LXT1001. To do this, the length of the PDC

- buffer, the buffer ID corresponding to the buffer, and any processing options are formatted into a 32-bit CPU register. The contents of the CPU register are then written to the device's *Transmit PDC Register*. This action has the effect of placing the PDC into the transmit command FIFO and setting a control bit in the FIFO identifying the command as a PDC.

- 7. When one or more commands are present in the transmit command FIFO, the bus master LXT1001 (BMC) is prompted to examine the FIFO and extract the first available command. In our example, the queue is assumed to be empty prior to the transmit request and thus the PDC is acted upon at the first available opportunity.

- 8. When the BMC looks at the command FIFO, it determines that the command is a PDC and moves it directly to the Command Execution Queue.

- The BMC now takes the PDC command and begins to execute it. It does so by decoding the BFID and BFLE fields (see the *Transmit PDC Register* for a discussion of the PDC command format).

- The BMC uses the BFID value in the PDC command to index the Transmit PDC Buffer Address Table and obtain the starting physical address of the buffer to be transferred to the LXT1001.

- Once the PDC has been decoded and the starting physical address obtained, the BMC instructs the PCI block to initiate a buffer data transfer to the TX FIFO.

- 12. The PCI block transfers the buffer data to the TX FIFO at the next available opportunity.

- 13. Once the packet is completely transferred to the data FIFO, the BMC signals the data FIFO that a complete packet has been transferred. The FIFO control logic then updates its pointers and signals the MAC that a packet is ready for transmission.

## Organization

The remainder of this section contains a pseudo-code driver for device initialization, packet transmission, packet reception, and interrupt processing. The intent of the pseudo-code driver is to demonstrate the basic concepts of programming the LXT1001 controller. It does not

represent the only way or necessarily the optimal way to operate the LXT1001 controller.

Initialization

This section contains a discussion of topics related to the initialization of the LXT1001. Example pseudo-code is also provided to demonstrate algorithms for initializing the LXT1001 for PIO, PDL, and PDC I/O methods.

#### Reset

The LXT1001 accepts two types of resets: <u>hard</u> reset and soft reset. A hard reset occurs when the PCI RST signal is asserted. The LXT1001 takes the following actions when performing a hard reset:

- All internal state machines of the LXT1001 are reset to their initial state.

- All internal registers of the LXT1001 are reset to their default value.

- All CSRs are reset to their default value.

- All PCI configuration space registers are reset to their default value.

- If an EEPROM is present, the LXT1001 reads the EEPROM and reloads selected CSRs and PCI configuration registers with the values read from EEPROM. For a detailed list of the registers loaded from EEPROM, see EEPROM Map on page 123.

A soft reset occurs when HOST software sets the SWRE bit in  $Mode\ Register-1$ . The LXT1001 takes the same actions for a soft reset as it does for a hard reset with one exception. During a soft reset, the LXT1001 does not reset the PCI configuration space registers. This is necessary to preserve the hardware resources assigned to the device by system BIOS and/or the operating system.

If HOST software attempts to access the LXT1001 while a hard or soft reset is in progress, the LXT1001 generates a PCI retry until the reset has completed. The LXT1001 indicates a PCI retry to the HOST/PCI bridge by asserting the STOP and deasserting TRDY, while keeping DEVSEL asserted during the first data phase of the access. Upon receiving this indication, the HOST/PCI bridge terminates the transaction. After waiting at least two PCI bus cycles, the HOST/PCI bridge will retry the access. The HOST/PCI bridge will continue retrying until the access succeeds. From the perspective of HOST software, the I/O instruction that generated the access blocks until the LXT1001's reset completes. To avoid the PCI bus and processor inefficiencies associated with PCI retries, after initiating a soft reset, HOST software should wait 20 ms before it

attempts any I/O to the LXT1001. Delaying 20 ms allows the LXT1001 to fully reset without having to issue PCI retries.

## Physical Layer Configuration and Status

The LXT1001 supports three physical layer interfaces: MII, GMII, and PCS. Regardless of the type of PHY present, HOST software interacts with PHY using the G/MII PHY Access Register. HOST software accesses PHY registers through this register. HOST software can assume the MII basic register set is present. The basic register set consists of the Control Register (register 0) and the Status Register (register 1). GMII-compliant PHYs have an extended basic register set that includes the Extended Status Register (register 15) in addition to the MII basic register set. If a PHY implements the Extended Status Register, it sets bit 8 in its Status Register. See IEEE Standard 802.3z, clause 22, for a detailed description of the basic, extended basic, and extended register sets. HOST software can also access vendor specific registers on the PHY using the G/MII PHY Access Register.

To read the *Status Register* of the PHY at address 2, for example, HOST software writes the following values to the *G/MII PHY Access Register*: GMRRIX = 1, GMCM = 0, GMPHAD = 2. HOST software then polls the register waiting for GMST = 0. When GMST = 0, the LXT1001 has completed the read operation and GMDA contains the value read from PHY. Write operations occur in a similar manner, except that HOST software puts the value to be written to the PHY register in the GMDA field when it initiates the request to the *G/MII PHY Access Register*.

At initialization time, HOST software is responsible for querying PHY to determine the type of PHY (MII or GMII), the current link speed, and the current duplex mode. Once this is determined, HOST software must set the appropriate values in the *G/MII Mode Register*. Setting the *G/MII Mode Register* determines how the LXT1001 interacts with PHY when transmitting and receiving packets.

The LXT1001 has the capability to poll PHY's *Status Register* and generate an interrupt when PHY's *Status Register* changes. This capability provides an efficient mechanism to detect changes in the physical layer status. When the interrupt occurs, HOST software can query PHY to determine the exact change in PHY status. HOST software enables this capability by setting the GMSTPOEN bit in *Mode Register* – 1 and the PHLASTMS bit in the *Interrupt Mask Register*.

#### **PDC Buffer Allocation**

When using the PDC I/O method, HOST software must allocate PDC buffers. HOST software allocates PDC buffers such that they have the following attributes:

- A PDC buffer must be at least 64 bytes long.

- A PDC buffer is physically contiguous. A buffer may span one or more page boundaries as long as the pages are physically contiguous.

- A PDC buffer is locked. The operating system will not swap the buffer to disk or move it a new location in physical memory.

- If possible, the starting address of a receive PDC buffer is on a cache line boundary and the buffer length is evenly divisible by the cache line size. This allows the LXT1001 to use memory write and invalidate commands when transferring data into the buffer.

When HOST software allocates a PDC buffer, it places the physical address of the PDC into either the Transmit PDC Buffer Address Table or the Receive PDC Buffer Address Table. Each of these tables hold a maximum of 64 PDCs. HOST software does not have to use every entry in the table.

#### **PDL Buffer Allocation**

When using the PDL I/O method, HOST software must allocate PDL buffers. HOST software allocates PDL buffers such that they have the following memory attributes:

- A PDL buffer is physically contiguous. A buffer may span a page boundary as long as the pages are physically contiguous.

- A PDL buffer is locked. The operating system will not swap the buffer to disk or move it to a new location in physical memory.

- At a minimum, the starting address of a PDL buffer must begin on a QWORD boundary. If possible, the starting address of PDLs should begin on a cache line boundary and the PDL buffer length is a multiple of cache lines. This allows the LXT1001 to use memory write and invalidate commands when transferring data into the PDL buffer. The use of memory write and invalidate commands improves system performance by eliminating unnecessary cache line writes to memory.

The fragment buffers pointed to by a PDL have the same memory attributes as a PDL with the following exception: fragments can be allocated on any byte boundary. This is necessary because fragments are typically allocated by upper layer software and are ephemeral in nature. Furthermore, the sum of the fragment lengths must be at least 64 bytes.

## **System Initialization Event Sequence**

At system initialization time, the following sequence of events occur.

- 1. The RST signal on the PCI bus is asserted, causing the LXT1001 to perform a hard reset.

- 2. HOST BIOS reads and writes the LXT1001's *PCI* Configuration Space Registers to determine the LXT1001's capabilities and resource requirements.

- HOST BIOS assigns resources to the LXT1001 by writing to the LXT1001's PCI Configuration Space Registers.

- If an expansion ROM is attached to the LXT1001, HOST BIOS shadows (copies) the expansion ROM image into system RAM.

- 5. If the LXT1001 is the active boot device, HOST BIOS invokes the expansion ROM image to bring the LXT1001 to a fully operational state.

- The operating system is loaded (either from a local disk or via the network connection provided by the LXT1001) and HOST BIOS gives control to the operating system.

- 7. The operating system loads and invokes the HOST device driver software for the LXT1001.

## Initialization Algorithm

The pseudo-code in **Table 2-1** demonstrates a typical algorithm HOST device driver software uses to bring the LXT1001 to a fully operational state. The "@" in the right-hand column indicates lines where HOST software accesses the LXT1001.

#### Table 2-1: Initialization Pseudo-Code

| (1)  | Function Initialize (TransmitPacketList)                                                                                             |   |

|------|--------------------------------------------------------------------------------------------------------------------------------------|---|

| (2)  | Locate the device using PCI services provided by BIOS or the operating system.                                                       | @ |

| (3)  | Query the CONTROLLER's PCI Configuration Registers to determine the IO Base Address, Memory Base Address, and Interrupt level.       | @ |

| (4)  | Select the desired mode settings via $Mode\ Register - 1\ (CSR00)$ and $Mode\ Register - 2\ (CSR001)$                                | @ |

| (5)  | If (the user has configured a locally administered address)                                                                          |   |

| (6)  | Program the locally administered address into the LAN Physical Address Registers (CSR42 and CSR43).                                  | @ |

| (7)  | Endif                                                                                                                                |   |

| (8)  | Query the PHY via <i>G/MII PHY Access Register</i> (CSR44) to determine the link status, duplex mode, and link speed.                | @ |

| (9)  | If (the current PHY mode is incompatible with the link speed, duplex mode, or autonegotiation modes settings the user has requested) |   |

| (10) | Reprogram the PHY to the user requested settings using CSR44.                                                                        | @ |

| (11) | If necessary, force the PHY to renegotiate with its link partner to reflect the new PHY settings.                                    | @ |

| (12) | Endif                                                                                                                                |   |

| (13) | Set the appropriate link speed and duplex mode values in the <i>G/MII Mode Register</i> (CSR45).                                     | @ |

| (14) | Perform the BIST test using the BIST Register in the PCI Configuration space.                                                        | @ |

| (15) | Call LoopbackTest(). See below.                                                                                                      | @ |

| (16) | If (the loopback test failed)                                                                                                        |   |

| (17) | <b>Return</b> indicating a fatal error occurred.                                                                                     | @ |

| (18) | Endif                                                                                                                                |   |

| (19) | If (a bus mastering method will be used to transmit packets)                                                                         |   |

| (20) | Read TXCMFECN from the <i>Command Status Register</i> (CSR51) and save the result in TxCommandsAvailable.                            | @ |

| (21) | Note: PDC and PDL modes are not mutually exclusive.                                                                                  |   |

| (22) | If (the PDC I/O method will be used to transmit packets)                                                                             |   |

| (23) | Call InitializePDCTransmit()                                                                                                         | @ |

| (24) | Endif                                                                                                                                |   |

| (25) | If (the PDL I/O method will be used to transmit packets)                                                                             |   |

| (26) | Call InitializePDLTransmit()                                                                                                         |   |

| (27) | Endif                                                                                                                                |   |

| (28) | Else                                                                                                                                 |   |

| (29) | Read TXFIDWCN from the TX FIFO DWORDs Free Register (CSR21).                                                                         | @ |

| (30) | Set BytesFreeInTxFIFO = TXFIDWCN * the number of bytes in a DWORD.                                                                   |   |

| (31) | Endif                                                                                                                                |   |

#### Table 2-1: Initialization Pseudo-Code – continued (32)If (PDC and/or PDL I/O method will be used for receiving) (33)Read RXCMFECN from the Command Status Register (CSR51) and save the result @ in RxCommandsAvailable. If (the PDC I/O method will be used to receive packets) (34)(35)Call InitializePDCReceive(RxCommandsAvailable). **(**a) (36)**Endif** If (the PDL I/O method will be used to receive packets) (37)Call InitializePDLReceive(RxCommandsAvailable). (38)@ (39)**Endif** (40)Set the interrupt mask RXPDMS in the Interrupt Mask Register (CSR30). This (a) will cause an interrupt each time the CONTROLLER has filled a PDL or PDC with a inbound packet. (41)Else using PIO method (42)Set the interrupt mask RXMS in the Interrupt Mask Register (CSR30). This will @ cause an interrupt when there is at least one packet in the RX FIFO. (43) **Endif** (44)Enable the transmitter and receiver by setting the TXEN and RXEN bits in (a) *Mode Register – 1* (CSR00). (45) Install the interrupt service routine to handle interrupts generated by the CONTROLLER. Enable the CONTROLLER's ability to generate an interrupt by setting the @ (46)INENMS bit in the *Interrupt Mask Register* (CSR30). (47) Return Success. (48) Endfunction (49)(50) Function LoopbackTest() (51)Enable MAC level loopback using the LPBKMD field in *Mode Register* – 2 (CSR01). @ (52)Enable the transmitter and receiver by setting the TXEN and RXEN bits in (a) *Mode Register – 1* (CSR00). (53)Transmit a packet to self using PIO method. @ (54)Poll the RXPKAV bit in the Chip Status Register (CSR11) until it is set. (a) (55)Receive the packet just transmitted using PIO receive. @ (56)**If** (errors occurred transmitting or receiving the loopback packet) (57)**Return** indicating PIO loopback test failed. Endif (58)(59)Build and issue a PDL receive command to the CONTROLLER. @ (60)Build and transmit a packet to self using PDL method. @ (61)Wait for RXDMDNCN field in the Command Status Register (CSR51) to (a) be non-zero. (62)Examine the packet just received. (a) **If** (errors occurred transmitting or receiving the loopback packet) (63)

| Tabl | e 2-1: Initialization Pseudo-Code – continued                                                                                                                                             |   |

|------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---|

| (64) | Return indicating PDL loopback test failed.                                                                                                                                               |   |

| (65) | Endif                                                                                                                                                                                     |   |

| (66) | Build and issue a PDC receive command to the CONTROLLER.                                                                                                                                  | @ |

| (67) | Build and transmit a packet to self using PDC method.                                                                                                                                     | @ |

| (68) | Wait for RXDMDNCN field in the <i>Command Status Register</i> (CSR51) to be non-zero.                                                                                                     | @ |

| (69) | Examine the packet just received.                                                                                                                                                         | @ |

| (70) | If (errors occurred transmitting or receiving the loopback packet)                                                                                                                        |   |

| (71) | Return indicating PDC loopback test failed.                                                                                                                                               |   |

| (72) | Endif                                                                                                                                                                                     |   |

| (73) | Disable the transmitter and receiver by clearing the TXEN and RXEN bits in $Mode\ Register-1\ (CSR00)$ .                                                                                  | @ |

| (74) | Return success.                                                                                                                                                                           |   |

| (75) | Endfunction                                                                                                                                                                               |   |

| (76) |                                                                                                                                                                                           |   |

| (77) | Function InitializePDCTransmit()                                                                                                                                                          |   |

| (78) | Initialize TableIndex $= 0$ .                                                                                                                                                             |   |

| (79) | For (the number of transmit PDC buffers to be allocated — up to the maximum of 64)                                                                                                        |   |

| (80) | Allocate a transmit PDC buffer.                                                                                                                                                           |   |

| (81) | Set the table index in the <i>Transmit PDC Buffer Address Table Register</i> (CSR02) to TableIndex.                                                                                       |   |

| (82) | Write the physical address of the transmit PDC buffer to the <i>Transmit PDC Buffer Address Registers</i> (CSR05 and CSR04). Writing to CSR04 causes the TBIX to automatically increment. | @ |

| (83) | Add the PDC to the TransmitPDCAvailableList.                                                                                                                                              |   |

| (84) | Increment TableIndex.                                                                                                                                                                     |   |

| (85) | Endfor                                                                                                                                                                                    |   |

| (86) | Endfunction                                                                                                                                                                               |   |

| (87) |                                                                                                                                                                                           |   |

| (88) | Function InitializePDCReceive(ReceiveCommandsAvailable)                                                                                                                                   |   |

| (89) | Initialize TableIndex $= 0$ .                                                                                                                                                             |   |

| (90) | For (for the number of PDC buffers to be allocated — up to the maximum of 64)                                                                                                             |   |

| (91) | Allocate a PDC buffer from the operating system.                                                                                                                                          |   |

| (92) | Set the table index in the <i>Receive PDC Buffer Address Table Register</i> (CSR06) to TableIndex.                                                                                        |   |

| (93) | Write the physical address of the receive PDC buffer to the <i>Receive PDC Buffer Address Registers</i> (CSR09 and CSR08). Writing to CSR08 causes the TBIX to automatically increment.   | @ |

| (94) | Increment TableIndex.                                                                                                                                                                     |   |

| (95) | If (RxCommandsAvailable)                                                                                                                                                                  |   |

Table 2-1: Initialization Pseudo-Code – continued

| (96)  | Call PDCQueueReceiveCommand(PDC, ReceiveCommandsAvailable) See Table 2-7                       |

|-------|------------------------------------------------------------------------------------------------|

| (97)  | Else                                                                                           |

| (98)  | Put the PDC on ReceivePDCAvailableList.                                                        |

| (99)  | Endif                                                                                          |

| (100) | Endfor                                                                                         |

| (101) | Endfunction                                                                                    |

| (102) |                                                                                                |

| (103) | Function InitializePDLTransmit()                                                               |

| (104) | For (the number of transmit PDL buffers to be allocated)                                       |

| (105) | Allocate a transmit PDL.                                                                       |

| (106) | Put the PDL on the TransmitPDLAvailableList.                                                   |

| (107) | Endfor                                                                                         |

| (108) | Endfunction                                                                                    |

| (109) |                                                                                                |

| (110) | Function InitializePDLReceive (Rx Commands Available)                                          |

| (111) | For (for the number of PDL buffers to be allocated)                                            |

| (112) | Allocate a PDL buffer from the operating system.                                               |

| (113) | If (RxCommandsAvailable)                                                                       |

| (114) | Allocate a ReceivePacketDescriptor from the operating system.                                  |

| (115) | Call PDLQueueReceiveCommand (PDL, ReceivePacketDescriptor, RxCommandsAvailable). See Table 2-6 |

| (116) | Else                                                                                           |

| (117) | Put the PDL on ReceivePDLAvailableList.                                                        |

| (118) | Endif                                                                                          |

| (119) | Endfor                                                                                         |

| (120) | Endfunction                                                                                    |

The initialization pseudo-code above and the pseudo-code for packet transmission, packet reception, and interrupt processing that follow constitute a pseudo driver of sorts.

The pseudo driver is based upon the following set of assumptions and design points:

- The driver will transmit packets using the PIO I/O method or a mixture of PDL/PDC I/O methods. It does not mix the PIO I/O method with other I/O methods.

- The driver receives packets using the PIO mode, PDL, or PDC I/O methods. It does not mix I/O methods when receiving.

- The protocol stack provides a list of packets to transmit rather than one packet.

- The driver indicates received packets to the protocol stack one at a time.

The Initialize() function is the top level function. It is responsible for bringing the device into an operational state. In a real driver, this function is called immediately after the driver is loaded. The major tasks it performs are as follows:

- Locating the device

- Initializing the PHY

- Performing a MAC loopback test using the PIO I/O method

- Allocating PDC buffers and initializing the PDC buffer address tables

- · Allocating PDLs

- Hooking an interrupt and enabling the LXT1001's ability to generate an interrupt for transmit and receive events

The variables used to model the LXT1001's transmitter and receiver states will be discussed in later sections.

## Transmit Packet Processing

This section contains discussions on topics related to transmitting packets with the LXT1001. Example pseudo-code is also provided to demonstrate algorithms for transmitting a packet in PIO, PDL, and PDC modes.

### **Transmit Packet Padding**

By default, when transmitting a packet that is smaller than the minimum packet size, the LXT1001 adds padding bytes to the end of the packet. For Ethernet, the minimum packet size is 60 bytes, excluding the CRC. The pad bytes added by the LXT1001 are included in the CRC calculation of the packet. The LXT1001's ability to pad undersized packets can be disabled by clearing the TXPPEN bit in *Mode Register – 1*. When this feature is disabled, it is the responsibility of HOST software to pad the packets prior to giving them to the LXT1001 for transmission. Failure to do so results in runt packets being transmitted on the network.

## **VLAN Tag Header Insertion**

The LXT1001 provides the capability to insert VLAN tag headers during the transmission of packets. See VLAN Support on page 40 for a detailed description of how to use this function.

#### **CRC Generation**

By default, the LXT1001 calculates and appends a 4-byte CRC to outbound packets. This capability can be disabled by clearing the TXCREN bit in *Mode Register – 1*. When TXCREN is cleared, it is the responsibility of HOST software to include a CRC in the packet data given to the LXT1001.

HOST software should ensure the TXCREN bit is set whenever it has enabled other LXT1001 features that cause the LXT1001 to insert or modify packet data prior to the packet's transmission. In particular, the TXCREN bit should be set when HOST software has enabled VLAN tag header insertion, or transmit packet padding. Failure to set the TXCREN in these circumstances results in a packet

containing an invalid CRC to be transmitted onto the network.

### **Transmit Completion Status**

The LXT1001 implements a "lying send" transmit policy. This means a packet is considered to be successfully transmitted as soon as it is copied into the LXT1001's TX FIFO. When using the PIO I/O method, this occurs as soon as HOST software has moved the packet into the TX FIFO. When using the PDL and PDC I/O methods, this occurs as soon as the LXT1001 has transferred the packet data into the TX FIFO. Ultimately, it is the responsibility of the protocols above the driver to ensure that packets are successfully transmitted to remote stations. If a packet is lost during transmission by the LXT1001, the protocol is responsible for recognizing that the packet is lost and effecting a corrective action (e.g., retransmit).

#### **Transmit Statistics**

The LXT1001 maintains the following packet transmission statistics: aFramesTransmittedOK, aSingleCollisionFrames, aMultipleCollisionFrames, Errored Transmit Packet Count, TCP/IP Non Ipv4 Packet Count, and Late Collision Count. The counts do not wrap. See **Table 4-1** for a detailed description of these statistics.

## Simultaneous Use of PDL, PDC, and PIO I/O Methods

The LXT1001 supports the use of PDL and PDC I/O methods simultaneously. When transferring data, HOST software indicates the desired data transfer method by the CSR used to initiate the transfer. For packet transmission using the PDC I/O method, HOST software initiates the process by writing to the *Transmit PDC Register*. If the HOST wishes to transmit a packet using the PDL method, it writes to the *Transmit PDL Address Register* instead.

Although intermixing of PDC and PDL transmit commands is directly supported by the LXT1001, intermixing of PIO with either PDC or PDL transfer methods is **not** directly supported. It is possible to intermix PIO with the other two transfer methods, however, careful coordination must be carried out to prevent simultaneous accesses to the TX FIFO by the LXT1001's System Interface Block and HOST software. More specifically, prior to initiating a transmission using the PIO method, HOST software must guarantee that all PDL and/or PDC transmit commands issued have been completed by the LXT1001. A PDL and PDC transmit command is considered completed when the LXT1001 has transferred the transmit packet data from

HOST memory into the LXT1001's TX FIFO and incremented the TXDMDNCN count in the *Command Status Register*.

## **Programmed Input/Output Method of Transmission**

PIO mode is often referred to as a slave mode. The two terms are used interchangeably in this document. In PIO mode, the HOST is responsible for effecting all packet data movement to and from the LXT1001.

Transmitting a packet using the PIO method is a four-step process:

- Determining the TX FIFO has enough free space to accommodate the transmit header and packet

- 2. Writing the transmit header to the TX FIFO

- 3. Writing the packet data to the TX FIFO

- 4. Issuing the transmit command

The LXT1001 maintains a count of the number of free DWORDs in the TX FIFO. The LXT1001 decrements the count as data is written to the FIFO, and increments the count as data is removed from the FIFO and transmitted.

HOST software ascertains this count by reading the *TX FIFO DWORDs Free Register*. If the TX FIFO does not contain enough free space to accommodate the packet, HOST software must wait until enough free space exists. HOST software waits by polling, retrying periodically, or by requesting an interrupt be generated when the TX FIFO hits a low watermark. Refer to the *TX FIFO Low Watermark Register* description for more information on how to generate a TX FIFO low watermark interrupt.

Once HOST software has determined the TX FIFO can accommodate the packet, it constructs the transmit header and writes it to the TX FIFO via the TX FIFO Write Register. Next, HOST software copies the data to the LXT1001's TX FIFO by sequencing through the packet data and writing it to the TX FIFO Write Register. HOST software then sets the SLMDTXCM bit in the Command Register to indicate the entire packet is in the TX FIFO and is ready for transmission. The LXT1001 transmits the packet data onto the network in the order that it is written to the TX FIFO Write Register.

The pseudo-code in **Table 2-2** demonstrates how to transmit a list of packets using the PIO data transfer method. Lines with an "@" in the right-hand column indicate an access to the LXT1001.

#### Table 2-2: PIO Transmit Pseudo-Code

- (1) Function PIOTransmitPacketList(TransmitPacketList)

- (2) Get the first packet from TransmitPacketList.

- (3) While (there is a packet to be transmitted)

- (4) PacketLength = the number of bytes in the packet.

- (5) Set RetryCount =  $MAX_RETRIES + 1$ .

- (6) **While** (BytesFreeInTxFIFO < PacketLength + number of bytes in the transmit header)

- (7) **If** (RetryCount = 0)

- (8) Set the transmit status code for the current and all remaining packets in TransmitPacketList to indicate they did not transmit.

- (9) **Return** out of TX FIFO resources.

- (10) **Endif**

- (11) Read TXFIDWCN from the TX FIFO DWORDs Free Register (CSR21).

- (12) Set BytesFreeInTxFIFO = TXFIDWCN \* the number of bytes in a DWORD.

- (13) Decrement RetryCount.

- (14) **Endwhile**

- (15) Determine the per packet processing options.

(a)

#### Table 2-2: PIO Transmit Pseudo-Code – continued

| (16) | Construct the FIFO Transmit Header using the PacketLength and per packet processing options.                                               |    |

|------|--------------------------------------------------------------------------------------------------------------------------------------------|----|

| (17) | Write the FIFO Transmit Header to the TX FIFO Write Register (CSR22).                                                                      | (a |

| (18) | For (each fragment in the packet)                                                                                                          |    |

| (19) | If (the fragment starting address is odd)                                                                                                  |    |

| (20) | Write the first BYTE of the fragment to the TX FIFO Write Register (CSR22).                                                                | @  |

| (21) | Endif                                                                                                                                      |    |

| (22) | If (the fragment starting address is not evenly divisible by the size of a DWORD)                                                          |    |

| (23) | Write the next WORD of the fragment to the <i>Transmit FIFO Write Register</i> (CSR22).                                                    | @  |

| (24) | Endif                                                                                                                                      |    |

| (25) | While (at least a DWORD remains in the fragment)                                                                                           |    |