# XaQti XQ11800FP 1000 Mbps Gigabit Ethernet Controller

# **Data Sheet**

Order Number: 11800-0998-08

Applies to XQ11800FP chip revisions C and subsequent spins

# Revision/Update History:

| Rev. 8    | September 29, 1998 | Production Chip release, enhanced features                   |

|-----------|--------------------|--------------------------------------------------------------|

| Rev. 7    | February, 1998     | Enhanced formatting, corrections, additional timing diagrams |

| Rev. 6    | August 28, 1997    | New Document                                                 |

| Revs. 1-5 | Various            | Internal Document                                            |

XaQti Corporation San Jose, California http://www.xaqti.com

#### September 1998

While XaQti believes that the information included in this publication is correct as of the date of publication, it is subject to change without notice.

XaQti assumes no liability, including patent or copyright infringement, for safe and use of XaQti products. No patent licenses are implied.

Patents Pending.

Copyright © XaQti Corporation, 1997, 1998. All rights reserved.

XaQti, XMAC II, GDK II, TrueSTATS and Network-on-a-CHIP are trademarks, or registered trademarks of XaQti Corporation

TRI-STATE is a registered trademark of National Semiconductor Corporation. All other trademarks and registered trademarks are the property of their respective owners.

# 1.0 Features

- Highly Integrated Gigabit Ethernet Media Access Controller (MAC) with on-chip transmit and receive FIFO's and 8B10B PCS Encoder/Decoder.

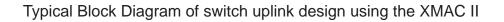

- High performance, single-chip Gigabit Ethernet solution for uplinks, gigabit switches, buffered repeaters, embedded point-to-point applications and network servers adapters.

- Network data bandwidth: 1000 Mbps in CSMA/CD (Half Duplex) and 2000 Mbps in Full Duplex.

- Capable of both Full Duplex and Half Duplex modes of operation, configurable in manual mode or automatically in response to Link Autonegotiation.

- Meets IEEE 802.3z Gigabit Ethernet and GMII (1000BASE-T) standard specifications and IEEE 802.3x specifications for frame-based flow control.

- The dual independent 32-bit 'streaming' FIFO interfaces allow single-cycle data transfers to support Full Duplex bandwidth for network data.

- Integrated, on-chip 8 KB Rx and 4 KB Tx FIFO's with programmable thresholds for minimizing overflows and underruns.

- Asynchronous FIFO interface operates between 33 MHz to 66 MHz Both 16-bit and 32-bit modes are supported and the FIFO interface can be hardware controlled without CPU intervention for the highest performance.

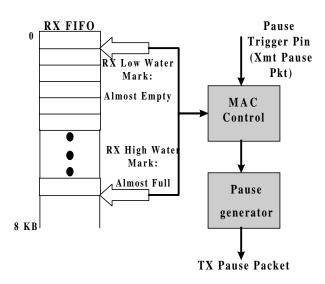

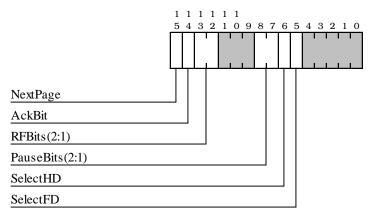

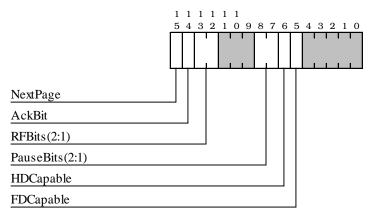

- Programmable PAUSE Frame-based flow control integrated with Rx FIFO watermarks for automatic pause and resumption. The Pause time value is configurable and all PHY PAUSE capabilities are supported (None, Asymmetric, Symmetric, Symmetric/Asymmetric). A Pause pin provides an integral host system pause capability.

- User configurable PHY interface supports the Gigabit Media Independent Interface (GMII) for 8-bit gigabit transceivers.

- The GMII interface is required for the emerging 1000BASE-T specifications (IEEE 802.3ab).

- 10-bit FC-0 PHY interface to: industry-standard 1.25 Gbps Gigabit Ethernet Transceiver (SERDES) devices.

- Supports fiber optic and short-haul copper media options (1000 BASE-SX, 1000BASE-CX, 1000BASE-LX)

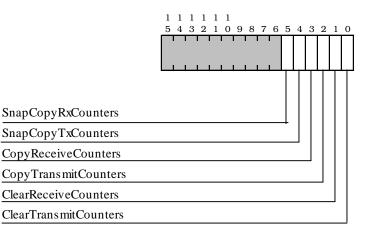

- TrueSTATS<sup>TM</sup> SNMP and RMON management counters provide accurate and atomic statistics even when accessed

under full gigabit traffic conditions without affecting performance.

- The 32-bit and 64-bit counters conform to IETF and ISO management standards and minimize counter 'wrapping'.

- Sixty-seven (67) status and configuration registers and the fifty-three (53) Etherstat counters can be addressed in 32bit or 16-bit format through a generic node processor interface.

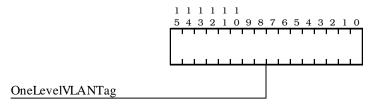

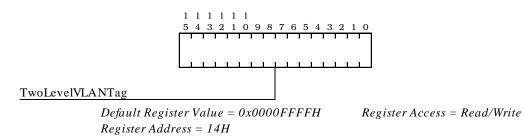

- Programmable options for the detection of one level and two level VLAN tag frames on the receive side.

- Unicast, multicast, broadcast and promiscuous address filtering capabilities.

- Packet Bursting and Carrier Extension in Half-duplex mode.

- Low-Voltage 0.35µ CMOS technology for 3.3V operation (5.0 V I/O tolerant).

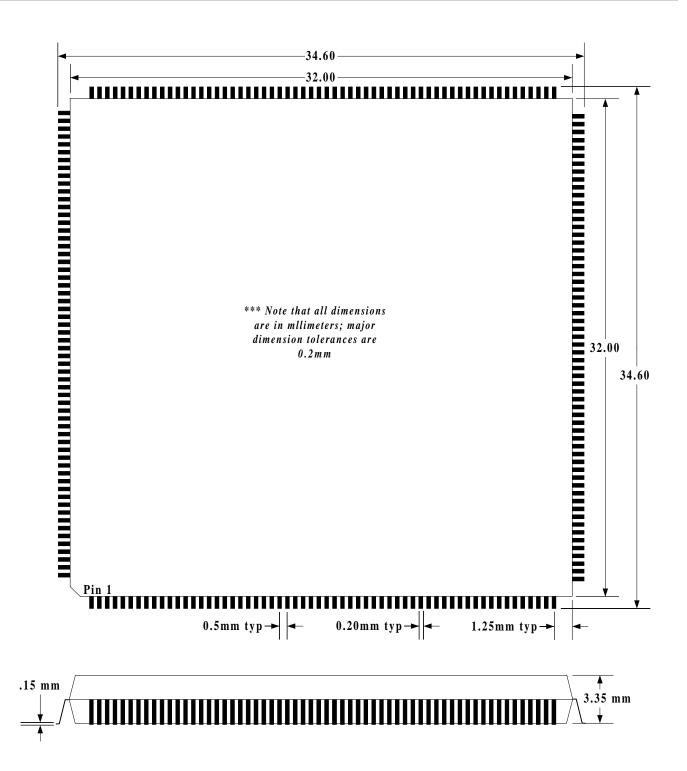

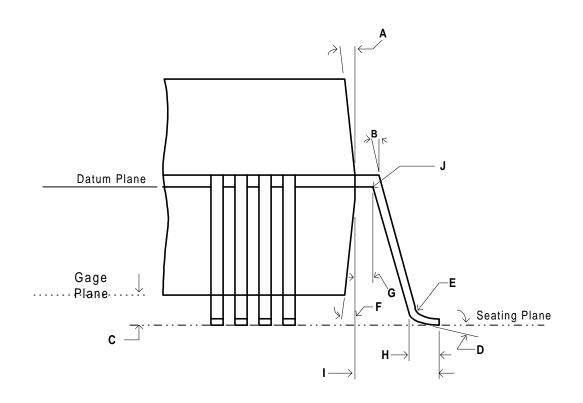

- Packaged in 240-pin PQFP.

# 2.0 General Description

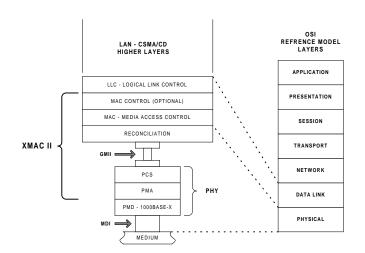

The XMACII is an advanced next-generation Gigabit Ethernet Media Access Controller for high performance 1000BASE applications such as switches, uplinks, buffered repeaters, point-to-point embedded applications and server adapters. The full-speed Ethernet Controller is both Full Duplex and Half Duplex capable, and integrates full support of PCS—8B10B Encoding/Decoding, Half Duplex and Full Duplex Link Autonegotiation. The Controller's Half Duplex mode of operation supports Carrier Extension and Packet Burst.

The Controller interfaces directly to 10-bit FC-0 SERDES 1.25 Gbps Gigabit Ethernet transceivers.

The XMACII controller includes integrated dual independent 8KB Receive and 4KB Transmit FIFO buffers with 32-bit wide buses that support 'bursting' and ensures 2 Gbps Full Duplex bandwidth in the most demanding network implementations. Programmable FIFO thresholds minimize overflows and underruns and can trigger automatic IEEE 802.3x Pause Frame-based flow control. Asymmetric or Symmetric Pause implementations can be implemented for full support of this specification.

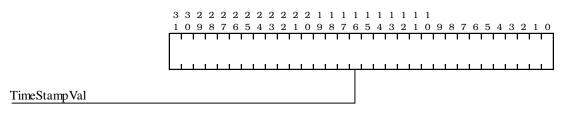

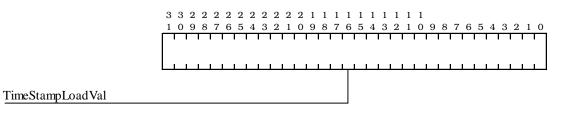

The granularity of the internal 32-bit 'timestamp' timer can be controlled through the external clock source and reset signal and can accept clock source signals from 1 to 31.25 Mhz.

The unique TrueSTATS<sup>TM</sup> SNMP and RMON management counter sets are accessible through a generic Node Processor interface which is also used for Controller mode programming. Transmit and Receive *Utilization Statistics* are constantly computed and instantly available. The TrueSTATS *shadow registers* design ensures atomic and accurate statistics even in the midst of full burst network activity and eliminates the inherent access latency problems of other MAC counter implementations. The full set of Etherstat MIB statistics counters conform to IETF and ISO specifications and are at least 32-bits wide to eliminate frequent counter 'wrapping'.

The XMACII includes sixty-seven (67) configuration and status registers and fifty-three (53) statistical counters. The registers and counters can be accessed by either 16-bit, or 32bit mode through the Node Processor interface.

The XMACII is rich in features, found in no other controllers for special traffic shaping and test applications. Sixteen internal address-matching registers are supplied to support Multicast applications or multiple users and a separate 64-bit hash filter is provided for less rigorous matching. If there is a match, the frame is received and signalled and the *MACAddress Match* signal is asserted. The Controller is capable of of transmitting and receiving 'Jumbo' packets for special server applications. The XMACII controller is fully compatible with the latest IEEE 802.3 specifications for Gigabit Ethernet, PCS, VLAN and Pause MAC-frame flow control.

The XaQti Gigabit Ethernet Controller is implemented in a low-power 3.3V CMOS device within a 240-pin PQFP package. The pins are 5.0V tolerant.

# 3.0 XMAC II Special and Unique Features

- On-chip address CAM-like registers provides 16 exact matches on address - each of which can be individually programmed. Indication of matches is provided even in promiscuous mode. One exact Source/Destination address pair may also be configured.

- A special register provides the source address of the latest 'good' received packet.

- 64-bit hash filter for multicast frames.

- Programmable frame-by-frame CRC append or disable; CRC check on Rx packets.

- Receive frame status is appended to the end of the received frame along with optional 32-bit timestamp.

- The internal 32-bit 'timestamp' timer can be controlled with an external clock source with a input signal range of 1 to 31.25 Mhz and can be reset externally.

- Two programmable VLAN registers Rx event counters correctly adjusted for new frame sizes - 1522 for one level VLAN, 1538 for two level VLAN.

- Interpacket Gap (IPG) can be adjusted for traffic shaping.

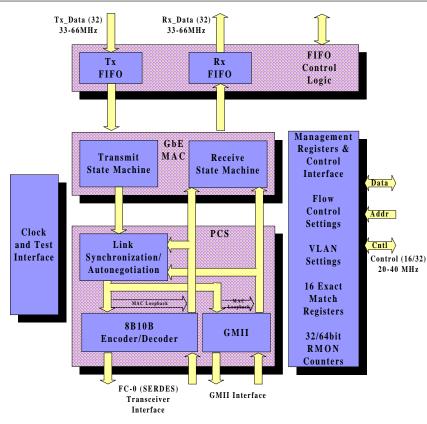

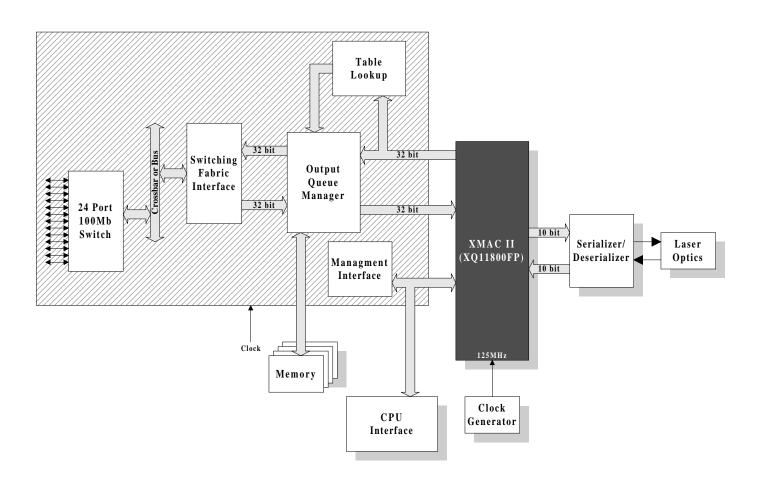

#### Figure 1 - XMAC II System Diagram

- Transmit and Receive Utilization continually computed.

- Capable of promiscuous mode operation for testers and special applications.

- Provides internal and external loopback options.

- Programmable options allow selective reception of all: MAC-Control frames; CRC and other error packets and transmission of MAC-Control frames and 'error' packets.

- *Transparent* mode allows transmission of characters in encoded/'unencoded' format on the transmit path with 8B10B PCS encoding but with preamble (SFD) on the receive path.

- Receive FIFO interface can also be tri-stated for multidevice interconnection.

- The Controller's Host Receive Ready signal enables the system to stop and start data transfer upon demand.

- Transmit and Receive status is automatically generated on a per-packet basis.

- Special options to *flush* the Tx and Rx FIFOs or the current Tx or Rx frames.

- Little or Big Endian byte ordering for the Host FIFO interface.

# 4.0 Pinout

This section describes the XQ11800FP signal pinouts and descriptions.

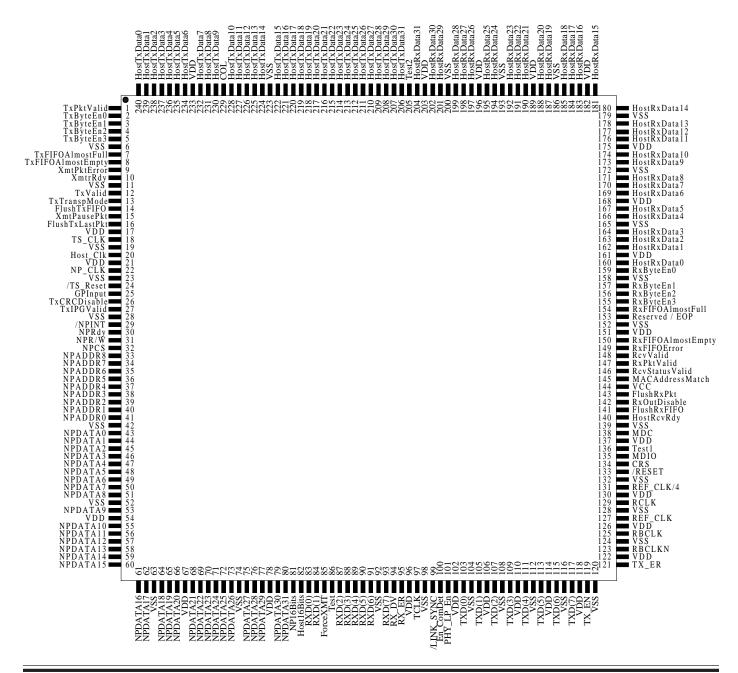

# 4.0.1 Chip Pinouts, GMII Mode PHY Interface

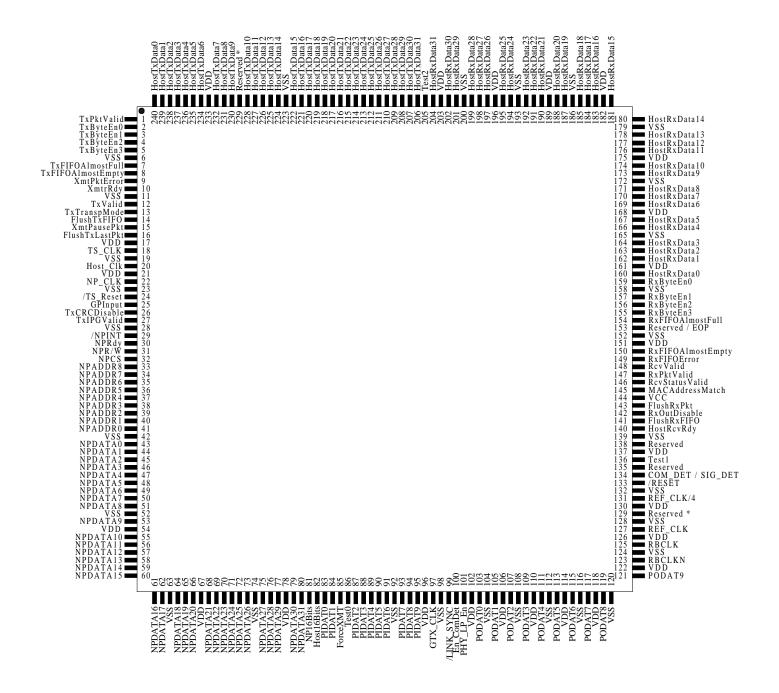

# 4.0.2 Chip Pinouts, FC-0 Mode PHY Interface

### 4.1 SIGNAL DESCRIPTIONS

The following abbreviations are used:

| Ι          | = | Input                                                                                |  |

|------------|---|--------------------------------------------------------------------------------------|--|

| 0          | = | Output                                                                               |  |

| I/O        | = | Input/Output                                                                         |  |

| TTL In     | = | TTL level input signal                                                               |  |

| TTL4       | = | TTL, 4mA output signal                                                               |  |

| TTL8       | = | TTL, 8mA output signal                                                               |  |

| CMOS2      | = | CMOS, 2mA output signal                                                              |  |

| CMOS4      | = | CMOS, 4mA output signal                                                              |  |

| CMOS8      | = | CMOS, 8mA output signal                                                              |  |

| Pull Up    | = | Pull up to $V_{DD}$ through resistor                                                 |  |

| OD         | = | Open Drain                                                                           |  |

| Tri        | = | Tri-stated TTL pins                                                                  |  |

| GND        | = | Connect to ground                                                                    |  |

| No connect | = | Must not be connected                                                                |  |

| Power      | = | Power Input, Refer to Section<br>9.2, Electrical and Environmental<br>Specifications |  |

## 4.2 XMAC II PIN LISTINGS

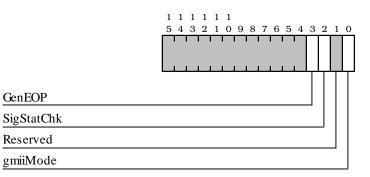

The following pages describe the signals used by the XQ11800FP. The XMAC II may be configured in either of two PHY interface modes. The PHY interface mode is determined by the *gmiiMode* bit (Bit #0) in the **Hardware Configuration** register.

If this bit is set to '1', then the GMII interface is selected for the XMACII PHY interface. This XMAC II Pin Listing for the GMII interface is provided in Section 4.2.1, immediately following.

If this bit is set to '0' (default), then the 10-bit, 125 MHz FC-0 interface is selected for the XMAC II PHY interface. The Pin Listings for the FC-0 PHY interface mode are listed separately in Section 4.2.2.

# 4.2.1 XMAC II PIN LISTING, GMII PHY INTERFACE MODE

| Pin# | Pin Name          | I/O | Туре      | Pin # | Pin Name | I/O | Туре     |

|------|-------------------|-----|-----------|-------|----------|-----|----------|

| 1    | TxPktValid        | Ι   | TTL In    | 41    | NPADDR0  | Ι   | TTL In   |

| 2    | TxByteEn0         | Ι   | TTL In    | 42    | VSS      | Ι   | Power    |

| 3    | TxByteEn1         | Ι   | TTL In    | 43    | NPDATA0  | I/O | TTL4 I/O |

| 4    | TxByteEn2         | Ι   | TTL In    | 44    | NPDATA1  | I/O | TTL4 I/O |

| 5    | TxByteEn3         | Ι   | TTL In    | 45    | NPDATA2  | I/O | TTL4 I/O |

| 6    | VSS               | Ι   | Power     | 46    | NPDATA3  | I/O | TTL4 I/O |

| 7    | TxFIFOAlmostFull  | 0   | CMOS4 Out | 47    | NPDATA4  | I/O | TTL4 I/O |

| 8    | TxFIFOAlmostEmpty | 0   | CMOS4 Out | 48    | NPDATA5  | I/O | TTL4 I/O |

| 9    | XmtPktError       | 0   | CMOS4 Out | 49    | NPDATA6  | I/O | TTL4 I/O |

| 10   | XmtrRdy           | 0   | CMOS8 Out | 50    | NPDATA7  | I/O | TTL4 I/O |

| 11   | VSS               | Ι   | Power     | 51    | NPDATA8  | I/O | TTL4 I/O |

| 12   | TxValid           | Ι   | TTL In    | 52    | VSS      | Ι   | Power    |

| 13   | TxTranspMode      | Ι   | TTL In    | 53    | NPDATA9  | I/O | TTL4 I/O |

| 14   | FlushTxFIFO       | Ι   | TTL In    | 54    | VDD      | Ι   | Power    |

| 15   | XmtPausePkt       | Ι   | TTL In    | 55    | NPDATA10 | I/O | TTL4 I/O |

| 16   | FlushTxLastPkt    | Ι   | TTL In    | 56    | NPDATA11 | I/O | TTL4 I/O |

| 17   | VDD               | Ι   | Power     | 57    | NPDATA12 | I/O | TTL4 I/O |

| 18   | TS_CLK            | Ι   | TTL In    | 58    | NPDATA13 | I/O | TTL4 I/O |

| 19   | VSS               | Ι   | Power     | 59    | NPDATA14 | I/O | TTL4 I/O |

| 20   | HOST_CLK          | Ι   | TTL In    | 60    | NPDATA15 | I/O | TTL4 I/O |

| 21   | VDD               | Ι   | Power     | 61    | NPDATA16 | I/O | TTL4 I/O |

| 22   | NP_CLK            | Ι   | TTL In    | 62    | NPDATA17 | I/O | TTL4 I/O |

| 23   | VSS               | Ι   | Power     | 63    | VSS      | Ι   | Power    |

| 24   | /TS_RESET         | Ι   | TTL In    | 64    | NPDATA18 | I/O | TTL4 I/O |

| 25   | GPINPUT           | Ι   | TTL In    | 65    | NPDATA19 | I/O | TTL4 I/O |

| 26   | TxCRCDisable      | Ι   | TTL In    | 66    | NPDATA20 | I/O | TTL4 I/O |

| 27   | TxIPGValid        | Ι   | TTL In    | 67    | VDD      | Ι   | Power    |

| 28   | VSS               | Ι   | Power     | 68    | NPDATA21 | I/O | TTL4 I/O |

| 29   | /NPINT            | 0   | CMOS OD   | 69    | NPDATA22 | I/O | TTL4 I/O |

| 30   | NPRDY             | 0   | CMOS4 Out | 70    | NPDATA23 | I/O | TTL4 I/O |

| 31   | NPR/W             | Ι   | TTL In    | 71    | NPDATA24 | I/O | TTL4 I/O |

| 32   | NPCS              | Ι   | TTL In    | 72    | NPDATA25 | I/O | TTL4 I/O |

| 33   | NPADDR8           | Ι   | TTL In    | 73    | NPDATA26 | I/O | TTL4 I/O |

| 34   | NPADDR7           | Ι   | TTL In    | 74    | VSS      | Ι   | Power    |

| 35   | NPADDR6           | Ι   | TTL In    | 75    | NPDATA27 | I/O | TTL4 I/O |

| 36   | NPADDR5           | Ι   | TTL In    | 76    | NPDATA28 | I/O | TTL4 I/O |

| 37   | NPADDR4           | Ι   | TTL In    | 77    | NPDATA29 | I/O | TTL4 I/O |

| 38   | NPADDR3           | Ι   | TTL In    | 78    | VDD      | Ι   | Power    |

| 39   | NPADDR2           | Ι   | TTL In    | 79    | NPDATA30 | I/O | TTL4 I/O |

| 40   | NPADDR1           | Ι   | TTL In    | 80    | NPDATA31 | I/O | TTL4 I/O |

# 4.2.1 XMAC II PIN LISTING, GMII MODE (CONT.)

| Pin# | Pin Name   | I/O | Туре       |

|------|------------|-----|------------|

| 81   | NP16Bits   | Ι   | TTL In     |

| 82   | Host16Bits | Ι   | TTL In     |

| 83   | RXD(0)     | Ι   | CMOS In    |

| 84   | RXD(1)     | Ι   | CMOS In    |

| 85   | ForceXmt   | Ι   | TTL In     |

| 86   | TEST0      | Ι   | GND        |

| 87   | RXD(2)     | Ι   | CMOS In    |

| 88   | RXD(3)     | Ι   | CMOS In    |

| 89   | RXD(4)     | Ι   | CMOS In    |

| 90   | RXD(5)     | Ι   | CMOS In    |

| 91   | RXD(6)     | Ι   | CMOS In    |

| 92   | VSS        | Ι   | Power      |

| 93   | RXD(7)     | Ι   | CMOS In    |

| 94   | RX_DV      | Ι   | CMOS In    |

| 95   | RX_ER      | Ι   | CMOS In    |

| 96   | VDD        | Ι   | Power      |

| 97   | TCLK       | 0   | CMOS16 Out |

| 98   | VSS        | Ι   | Power      |

| 99   | /LINK_SYNC | 0   | CMOS4 Out  |

| 100  | Reserved   | -   | No Connect |

| 101  | Reserved   | -   | No Connect |

| 102  | VDD        | Ι   | Power      |

| 103  | TXD(0)     | 0   | CMOS16 Out |

| 104  | VSS        | Ι   | Power      |

| 105  | TXD(1)     | 0   | CMOS16 Out |

| 106  | VDD        | Ι   | Power      |

| 107  | TXD(2)     | 0   | CMOS16 Out |

| 108  | VSS        | Ι   | Power      |

| 109  | TXD(3)     | 0   | CMOS16 Out |

| 110  | VDD        | Ι   | Power      |

| 111  | TXD(4)     | 0   | CMOS16 Out |

| 112  | VSS        | Ι   | Power      |

| 113  | TXD(5)     | 0   | CMOS16 Out |

| 114  | VDD        | Ι   | Power      |

| 115  | TXD(6)     | 0   | CMOS16 Out |

| 116  | VSS        | Ι   | Power      |

| 117  | TXD(7)     | 0   | CMOS16 Out |

| 118  | VDD        | Ι   | Power      |

| 119  | TX_EN      | 0   | CMOS16 Out |

| 120  | VSS        | Ι   | Power      |

| Pin# | Pin Name              | I∕O | Type       |

|------|-----------------------|-----|------------|

| 121  | TX ER                 | 0   | CMOS16 Out |

| 122  | VDD                   | Ι   | Power      |

| 123  | Reserved *            | Ι   | GND        |

| 124  | VSS                   | Ι   | Power      |

| 125  | Reserved <sup>*</sup> | I   | GND        |

| 126  | VDD                   | Ι   | Power      |

| 127  | REF_CLK               | Ι   | TTL In     |

| 128  | VSS                   | Ι   | Power      |

| 129  | RCLK                  | Ι   | TTL In     |

| 130  | VDD                   | Ι   | Power      |

| 131  | REF_CLK/4             | 0   | CMOS4 Out  |

| 132  | VSS                   | Ι   | Power      |

| 133  | /RESET                | Ι   | TTL In     |

| 134  | CRS                   | Ι   | CMOS In    |

| 135  | MDIO                  | I/O | CMOS       |

| 136  | TEST1                 | Ι   | GND        |

| 137  | VDD                   | Ι   | Power      |

| 138  | MDC                   | 0   | CMOS2 Out  |

| 139  | VSS                   | Ι   | Power      |

| 140  | HostRcvRdy            | Ι   | TTL In     |

| 141  | FlushRxFIFO           | Ι   | TTL In     |

| 142  | RxOutDisable          | Ι   | TTL In     |

| 143  | FlushRxPkt            | Ι   | TTL In     |

| 144  | VCC                   | Ι   | Power      |

| 145  | MACAddressMatch       | 0   | CMOS8 Out  |

| 146  | RcvStatus Valid       | 0   | CMOS8 Out  |

| 147  | RxPkt Valid           | 0   | CMOS8 Out  |

| 148  | Rcv Valid             | 0   | CMOS8 Out  |

| 149  | RxFIFOError           | 0   | CMOS4 Out  |

| 150  | RxFIFOAlmostEmpty     | 0   | CMOS4 Out  |

| 151  | VDD                   | 0   | Power      |

| 152  | VSS                   | Ι   | Power      |

| 153  | Reserved / EOP        | 0   | CMOS8 Out  |

| 154  | RxFIFOAlmostFull      | 0   | CMOS4 Out  |

| 155  | RxByteEn3             | 0   | TTL8 Tri   |

| 156  | RxByteEn2             | 0   | TTL8 Tri   |

| 157  | RxByteEn1             | 0   | TTL8 Tri   |

| 158  | VSS                   | Ι   | Power      |

| 159  | RxByteEn0             | 0   | TTL8 Tri   |

| 160  | HostRxData0           | 0   | TTL8 Tri   |

# 4.2.1 XMAC II PIN LISTING, GMII MODE (CONT.)

| wer<br>.8 Tri<br>.8 Tri<br>.8 Tri<br>.8 Tri<br>.8 Tri<br>.8 Tri<br>.8 Tri<br>wer |

|----------------------------------------------------------------------------------|

| .8 Tri<br>.8 Tri<br>.8 Tri<br>.8 Tri<br>wer<br>.8 Tri<br>.8 Tri                  |

| _8 Tri<br>_8 Tri<br>wer<br>_8 Tri<br>_8 Tri                                      |

| .8 Tri<br>wer<br>.8 Tri<br>.8 Tri                                                |

| wer<br>.8 Tri<br>.8 Tri                                                          |

| .8 Tri<br>.8 Tri                                                                 |

| .8 Tri                                                                           |

|                                                                                  |

| wei                                                                              |

| .8 Tri                                                                           |

| .8 Tri                                                                           |

| .8 Tri                                                                           |

| wer                                                                              |

| .8 Tri                                                                           |

| .8 Tri                                                                           |

|                                                                                  |

| wer                                                                              |

| .8 Tri                                                                           |

| .8 Tri                                                                           |

| .8 Tri                                                                           |

| wer                                                                              |

| .8 Tri                                                                           |

| .8 Tri                                                                           |

| wer                                                                              |

| .8 Tri                                                                           |

| .8 Tri                                                                           |

| .8 Tri                                                                           |

| wer                                                                              |

| .8 Tri                                                                           |

| .8 Tri                                                                           |

| wer                                                                              |

| .8 Tri                                                                           |

| .8 Tri                                                                           |

| .8 Tri                                                                           |

| wer                                                                              |

| .8 Tri                                                                           |

| .8 Tri                                                                           |

| wer                                                                              |

| .8 Tri                                                                           |

| .8 Tri                                                                           |

| .8 Tri                                                                           |

| wer                                                                              |

|                                                                                  |

| Pin # | Pin Name     | I/O | Туре     |

|-------|--------------|-----|----------|

| 201   | HostRxData29 | 0   | TTL8 Tri |

| 202   | HostRxData30 | 0   | TTL8 Tri |

| 203   | VDD          | Ι   | Power    |

| 204   | HostRxData31 | 0   | TTL8 Tri |

| 205   | TEST2        | Ι   | GND      |

| 206   | HostTxData31 | Ι   | TTL In   |

| 207   | HostTxData30 | Ι   | TTL In   |

| 208   | HostTxData29 | Ι   | TTL In   |

| 209   | HostTxData28 | Ι   | TTL In   |

| 210   | HostTxData27 | Ι   | TTL In   |

| 211   | HostTxData26 | Ι   | TTL In   |

| 212   | HostTxData25 | Ι   | TTL In   |

| 213   | HostTxData24 | Ι   | TTL In   |

| 214   | HostTxData23 | Ι   | TTL In   |

| 215   | HostTxData22 | Ι   | TTL In   |

| 216   | HostTxData21 | Ι   | TTL In   |

| 217   | HostTxData20 | Ι   | TTL In   |

| 218   | HostTxData19 | Ι   | TTL In   |

| 219   | HostTxData18 | Ι   | TTL In   |

| 220   | HostTxData17 | Ι   | TTL In   |

| 221   | HostTxData16 | Ι   | TTL In   |

| 222   | HostTxData15 | Ι   | TTL In   |

| 223   | VSS          | Ι   | Power    |

| 224   | HostTxData14 | Ι   | TTL In   |

| 225   | HostTxData13 | Ι   | TTL In   |

| 226   | HostTxData12 | Ι   | TTL In   |

| 227   | HostTxData11 | Ι   | TTL In   |

| 228   | HostTxData10 | Ι   | TTL In   |

| 229   | COL          | Ι   | CMOS In  |

| 230   | HostTxData9  | Ι   | TTL In   |

| 231   | HostTxData8  | Ι   | TTL In   |

| 232   | HostTxData7  | Ι   | TTL In   |

| 233   | VDD          | Ι   | Power    |

| 234   | HostTxData6  | Ι   | TTL In   |

| 235   | HostTxData5  | Ι   | TTL In   |

| 236   | HostTxData4  | Ι   | TTL In   |

| 237   | HostTxData3  | Ι   | TTL In   |

| 238   | HostTxData2  | Ι   | TTL In   |

| 239   | HostTxData1  | Ι   | TTL In   |

| 240   | HostTxData0  | Ι   | TTL In   |

# 4.2.2 XMAC II PIN LISTING, 10-BIT FC-0 PHY INTERFACE MODE

| Pin# | Pin Name          | I/O | Туре      |

|------|-------------------|-----|-----------|

| 1    | TxPktValid        | I   | TTL In    |

| 2    | TxByteEn0         | I   | TTL In    |

| - 3  | TxByteEn1         | I   | TTL In    |

| 4    | TxByteEn2         | Ι   | TTL In    |

| 5    | TxByteEn3         | Ι   | TTL In    |

| 6    | VSS               | Ι   | Power     |

| 7    | TxFIFOAlmostFull  | 0   | CMOS4 Out |

| 8    | TxFIFOAlmostEmpty | 0   | CMOS4 Out |

| 9    | XmtPktError       | 0   | CMOS4 Out |

| 10   | XmtrRdy           | 0   | CMOS8 Out |

| 11   | VSS               | Ι   | Power     |

| 12   | TxValid           | Ι   | TTL In    |

| 13   | TxTranspMode      | Ι   | TTL In    |

| 14   | FlushTxFIFO       | Ι   | TTL In    |

| 15   | XmtPausePkt       | Ι   | TTL In    |

| 16   | FlushTxLastPkt    | Ι   | TTL In    |

| 17   | VDD               | Ι   | Power     |

| 18   | TS_CLK            | Ι   | TTL In    |

| 19   | VSS               | Ι   | Power     |

| 20   | HOST_CLK          | Ι   | TTL In    |

| 21   | VDD               | Ι   | Power     |

| 22   | NP_CLK            | Ι   | TTL In    |

| 23   | VSS               | Ι   | Power     |

| 24   | /TS_RESET         | Ι   | TTL In    |

| 25   | GPINPUT           | Ι   | TTL In    |

| 26   | TxCRCDisable      | Ι   | TTL In    |

| 27   | TxIPGValid        | Ι   | TTL In    |

| 28   | VSS               | Ι   | Power     |

| 29   | /NPINT            | 0   | CMOS OD   |

| 30   | NPRDY             | 0   | CMOS4 Out |

| 31   | NPR/W             | Ι   | TTL In    |

| 32   | NPCS              | Ι   | TTL In    |

| 33   | NPADDR8           | Ι   | TTL In    |

| 34   | NPADDR7           | Ι   | TTL In    |

| 35   | NPADDR6           | Ι   | TTL In    |

| 36   | NPADDR5           | Ι   | TTL In    |

| 37   | NPADDR4           | Ι   | TTL In    |

| 38   | NPADDR3           | Ι   | TTL In    |

| 39   | NPADDR2           | Ι   | TTL In    |

| 40   | NPADDR1           | Ι   | TTL In    |

| Pin # | Pin Name | I/O | Туре     |

|-------|----------|-----|----------|

| 41    | NPADDR0  | I   | TTL In   |

| 42    | VSS      | Ι   | Power    |

| 43    | NPDATA0  | I/O | TTL4 I/O |

| 44    | NPDATA1  | I/O | TTL4 I/O |

| 45    | NPDATA2  | I/O | TTL4 I/O |

| 46    | NPDATA3  | I/O | TTL4 I/O |

| 47    | NPDATA4  | I/O | TTL4 I/O |

| 48    | NPDATA5  | I/O | TTL4 I/O |

| 49    | NPDATA6  | I/O | TTL4 I/O |

| 50    | NPDATA7  | I/O | TTL4 I/O |

| 51    | NPDATA8  | I/O | TTL4 I/O |

| 52    | VSS      | Ι   | Power    |

| 53    | NPDATA9  | I/O | TTL4 I/O |

| 54    | VDD      | Ι   | Power    |

| 55    | NPDATA10 | I/O | TTL4 I/O |

| 56    | NPDATA11 | I/O | TTL4 I/O |

| 57    | NPDATA12 | I/O | TTL4 I/O |

| 58    | NPDATA13 | I/O | TTL4 I/O |

| 59    | NPDATA14 | I/O | TTL4 I/O |

| 60    | NPDATA15 | I/O | TTL4 I/O |

| 61    | NPDATA16 | I/O | TTL4 I/O |

| 62    | NPDATA17 | I/O | TTL4 I/O |

| 63    | VSS      | Ι   | Power    |

| 64    | NPDATA18 | I/O | TTL4 I/O |

| 65    | NPDATA19 | I/O | TTL4 I/O |

| 66    | NPDATA20 | I/O | TTL4 I/O |

| 67    | VDD      | Ι   | Power    |

| 68    | NPDATA21 | I/O | TTL4 I/O |

| 69    | NPDATA22 | I/O | TTL4 I/O |

| 70    | NPDATA23 | I/O | TTL4 I/O |

| 71    | NPDATA24 | I/O | TTL4 I/O |

| 72    | NPDATA25 | I/O | TTL4 I/O |

| 73    | NPDATA26 | I/O | TTL4 I/O |

| 74    | VSS      | Ι   | Power    |

| 75    | NPDATA27 | I/O | TTL4 I/O |

| 76    | NPDATA28 | I/O | TTL4 I/O |

| 77    | NPDATA29 | I/O | TTL4 I/O |

| 78    | VDD      | Ι   | Power    |

| 79    | NPDATA30 | I/O | TTL4 I/O |

| 80    | NPDATA31 | I/O | TTL4 I/O |

# 4.2.2 XMAC II PIN LISTING, FC-0 PHY MODE (CONT.)

| Pin# | Pin Name   | I/O | Туре       |

|------|------------|-----|------------|

| 81   | NP16Bits   | I   | TTL In     |

| 82   | Host16Bits | Ι   | TTL In     |

| 83   | PIDAT0     | Ι   | CMOS In    |

| 84   | PIDAT1     | Ι   | CMOS In    |

| 85   | ForceXmt   | Ι   | TTL In     |

| 86   | TEST0      | Ι   | GND        |

| 87   | PIDAT2     | Ι   | CMOS In    |

| 88   | PIDAT3     | Ι   | CMOS In    |

| 89   | PIDAT4     | Ι   | CMOS In    |

| 90   | PIDAT5     | Ι   | CMOS In    |

| 91   | PIDAT6     | Ι   | CMOS In    |

| 92   | VSS        | Ι   | Power      |

| 93   | PIDAT7     | Ι   | CMOS In    |

| 94   | PIDAT8     | Ι   | CMOS In    |

| 95   | PIDAT9     | Ι   | CMOS In    |

| 96   | VDD        | Ι   | Power      |

| 97   | GTX_CLK    | 0   | CMOS16 Out |

| 98   | VSS        | Ι   | Power      |

| 99   | /LINK_SYNC | 0   | CMOS4 Out  |

| 100  | EN_COMDET  | 0   | CMOS4 Out  |

| 101  | PHY_LP_EN  | 0   | CMOS2 Out  |

| 102  | VDD        | Ι   | Power      |

| 103  | PODAT0     | 0   | CMOS16 Out |

| 104  | VSS        | Ι   | Power      |

| 105  | PODAT1     | 0   | CMOS16 Out |

| 106  | VDD        | Ι   | Power      |

| 107  | PODAT2     | 0   | CMOS16 Out |

| 108  | VSS        | Ι   | Power      |

| 109  | PODAT3     | 0   | CMOS16 Out |

| 110  | VDD        | Ι   | Power      |

| 111  | PODAT4     | 0   | CMOS16 Out |

| 112  | VSS        | Ι   | Power      |

| 113  | PODAT5     | 0   | CMOS16 Out |

| 114  | VDD        | Ι   | Power      |

| 115  | PODAT6     | 0   | CMOS16 Out |

| 116  | VSS        | Ι   | Power      |

| 117  | PODAT7     | 0   | CMOS16 Out |

| 118  | VDD        | Ι   | Power      |

| 119  | PODAT8     | 0   | CMOS16 Out |

| 120  | VSS        | Ι   | Power      |

| Pin# | Pin Name               | I∕O | Туре       |

|------|------------------------|-----|------------|

| 121  | PODAT9                 | 0   | CMOS16 Out |

| 122  | VDD                    | I   | Power      |

| 123  | RBCLKN                 | I   | TTL In     |

| 124  | VSS                    | I   | Power      |

| 125  | RBCLK                  | I   | TTL In     |

| 126  | VDD                    | I   | Power      |

| 127  | REF_CLK                | Ι   | TTL In     |

| 128  | VSS                    | Ι   | Power      |

| 129  | Reserved (*)           | Ι   | GND        |

| 130  | VDD                    | Ι   | Power      |

| 131  | REF_CLK/4              | 0   | CMOS4 Out  |

| 132  | VSS                    | Ι   | Power      |

| 133  | /RESET                 | Ι   | TTL In     |

| 134  | COM_DET / SIG_DET      | Ι   | CMOS In    |

| 135  | Reserved               | -   | Pull Up    |

| 136  | TEST1                  | Ι   | GND        |

| 137  | VDD                    | Ι   | Power      |

| 138  | Reserved               | -   | No Connect |

| 139  | VSS                    | Ι   | Power      |

| 140  | HostRcvRdy             | Ι   | TTL In     |

| 141  | FlushRxFIFO            | Ι   | TTL In     |

| 142  | RxOutDisable           | Ι   | TTL In     |

| 143  | FlushRxPkt             | Ι   | TTL In     |

| 144  | VCC                    | Ι   | Power      |

| 145  | MACAddressMatch        | 0   | CMOS8 Out  |

| 146  | <b>RcvStatus Valid</b> | 0   | CMOS8 Out  |

| 147  | RxPktValid             | 0   | CMOS8 Out  |

| 148  | RcvValid               | 0   | CMOS8 Out  |

| 149  | RxFIFOError            | 0   | CMOS4 Out  |

| 150  | RxFIFOAlmostEmpty      | 0   | CMOS4 Out  |

| 151  | VDD                    | 0   | Power      |

| 152  | VSS                    | Ι   | Power      |

| 153  | Reserved / EOP         | 0   | CMOS8 Out  |

| 154  | RxFIFOAlmostFull       | 0   | CMOS4 Out  |

| 155  | RxByteEn3              | 0   | TTL8 Tri   |

| 156  | RxByteEn2              | 0   | TTL8 Tri   |

| 157  | RxByteEn1              | 0   | TTL8 Tri   |

| 158  | VSS                    | Ι   | Power      |

| 159  | RxByteEn0              | 0   | TTL8 Tri   |

| 160  | HostRxData0            | 0   | TTL8 Tri   |

# 4.2.2 XMAC II PIN LISTING , FC-0 PHY MODE(CONT.)

| Pin # | Pin Name     | I/O | Туре     |

|-------|--------------|-----|----------|

| 161   | VDD          | Ι   | Power    |

| 162   | HostRxData1  | 0   | TTL8 Tri |

| 163   | HostRxData2  | 0   | TTL8 Tri |

| 164   | HostRxData3  | 0   | TTL8 Tri |

| 165   | VSS          | Ι   | Power    |

| 166   | HostRxData4  | 0   | TTL8 Tri |

| 167   | HostRxData5  | 0   | TTL8 Tri |

| 168   | VDD          | Ι   | Power    |

| 169   | HostRxData6  | 0   | TTL8 Tri |

| 170   | HostRxData7  | 0   | TTL8 Tri |

| 171   | HostRxData8  | 0   | TTL8 Tri |

| 172   | VSS          | Ι   | Power    |

| 173   | HostRxData9  | 0   | TTL8 Tri |

| 174   | HostRxData10 | 0   | TTL8 Tri |

| 175   | VDD          | Ι   | Power    |

| 176   | HostRxData11 | 0   | TTL8 Tri |

| 177   | HostRxData12 | 0   | TTL8 Tri |

| 178   | HostRxData13 | 0   | TTL8 Tri |

| 179   | VSS          | Ι   | Power    |

| 180   | HostRxData14 | 0   | TTL8 Tri |

| 181   | HostRxData15 | 0   | TTL8 Tri |

| 182   | VDD          | Ι   | Power    |

| 183   | HostRxData16 | 0   | TTL8 Tri |

| 184   | HostRxData17 | 0   | TTL8 Tri |

| 185   | HostRxData18 | 0   | TTL8 Tri |

| 186   | VSS          | Ι   | Power    |

| 187   | HostRxData19 | 0   | TTL8 Tri |

| 188   | HostRxData20 | 0   | TTL8 Tri |

| 189   | VDD          | Ι   | Power    |

| 190   | HostRxData21 | 0   | TTL8 Tri |

| 191   | HostRxData22 | 0   | TTL8 Tri |

| 192   | HostRxData23 | 0   | TTL8 Tri |

| 193   | VSS          | Ι   | Power    |

| 194   | HostRxData24 | 0   | TTL8 Tri |

| 195   | HostRxData25 | 0   | TTL8 Tri |

| 196   | VDD          | Ι   | Power    |

| 197   | HostRxData26 | 0   | TTL8 Tri |

| 198   | HostRxData27 | 0   | TTL8 Tri |

| 199   | HostRxData28 | 0   | TTL8 Tri |

| 200   | VSS          | I   | Power    |

| Pin # | Pin Name     | I/O | Туре     |

|-------|--------------|-----|----------|

| 201   | HostRxData29 | 0   | TTL8 Tri |

| 202   | HostRxData30 | Ο   | TTL8 Tri |

| 203   | VDD          | Ι   | Power    |

| 204   | HostRxData31 | Ο   | TTL8 Tri |

| 205   | TEST2        | Ι   | GND      |

| 206   | HostTxData31 | Ι   | TTL In   |

| 207   | HostTxData30 | Ι   | TTL In   |

| 208   | HostTxData29 | Ι   | TTL In   |

| 209   | HostTxData28 | Ι   | TTL In   |

| 210   | HostTxData27 | Ι   | TTL In   |

| 211   | HostTxData26 | Ι   | TTL In   |

| 212   | HostTxData25 | Ι   | TTL In   |

| 213   | HostTxData24 | Ι   | TTL In   |

| 214   | HostTxData23 | Ι   | TTL In   |

| 215   | HostTxData22 | Ι   | TTL In   |

| 216   | HostTxData21 | Ι   | TTL In   |

| 217   | HostTxData20 | Ι   | TTL In   |

| 218   | HostTxData19 | Ι   | TTL In   |

| 219   | HostTxData18 | Ι   | TTL In   |

| 220   | HostTxData17 | Ι   | TTL In   |

| 221   | HostTxData16 | Ι   | TTL In   |

| 222   | HostTxData15 | Ι   | TTL In   |

| 223   | VSS          | Ι   | Power    |

| 224   | HostTxData14 | Ι   | TTL In   |

| 225   | HostTxData13 | Ι   | TTL In   |

| 226   | HostTxData12 | Ι   | TTL In   |

| 227   | HostTxData11 | Ι   | TTL In   |

| 228   | HostTxData10 | Ι   | TTL In   |

| 229   | Reserved (*) | Ι   | GND      |

| 230   | HostTxData9  | Ι   | TTL In   |

| 231   | HostTxData8  | Ι   | TTL In   |

| 232   | HostTxData7  | Ι   | TTL In   |

| 233   | VDD          | Ι   | Power    |

| 234   | HostTxData6  | Ι   | TTL In   |

| 235   | HostTxData5  | Ι   | TTL In   |

| 236   | HostTxData4  | Ι   | TTL In   |

| 237   | HostTxData3  | Ι   | TTL In   |

| 238   | HostTxData2  | Ι   | TTL In   |

| 239   | HostTxData1  | Ι   | TTL In   |

| 240   | HostTxData0  | Ι   | TTL In   |

#### 4.3 PIN COUNT

Pin Count, GMII Mode PHY Interface

| Туре                               | Total |

|------------------------------------|-------|

| Host Processor I/F (Tx & Rx FIFOs) | 98    |

| Node Processor I/F                 | 45    |

| GMII PHY                           | 26    |

| Clock/Control/Test                 | 12    |

| Total I/O                          | 181   |

| V <sub>SS</sub> (Ground)           | 29    |

| V <sub>DD</sub>                    | 24    |

| V <sub>CC</sub>                    | 1     |

| Reserved                           | 5     |

| Total                              | 240   |

Pin Count, 10-bit FC-0 Transceiver Mode PHY Interface

| Туре                               | Total |

|------------------------------------|-------|

| Host Processor I/F (Tx & Rx FIFOs) | 98    |

| Node Processor I/F                 | 45    |

| 10-bit PHY (SerDes)                | 27    |

| Clock/Control/Test                 | 12    |

| Total I/O                          | 182   |

| V <sub>SS</sub> (Ground)           | 29    |

| V <sub>DD</sub>                    | 24    |

| V <sub>CC</sub>                    | 1     |

| Reserved                           | 4     |

| Total                              | 240   |

#### 4.4 CONNECTION RULES:

- All reserved pins must remain unconnected (except as noted with the asterik \*).

- Test pins must be connected to Ground.

# 4.5 XMAC II PIN DESCRIPTIONS

| Interface | Signal             | I/O | Signal Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

|-----------|--------------------|-----|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Host (Tx) | HostTxData(31:0)   | Ι   | These input pins provide the 32-bit data that will be clocked into the transmit FIFO on the rising edge of the $HOST\_CLK$ . $TxValid$ , $TxPktValid$ and $XmtrRdy$ signals should be asserted for this 32-bit data to be clocked into the transmit FIFO. In 16-bit mode, $HostTxData$ (31:16) needs to be connected to V <sub>CC</sub> through a resistor.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|           | TxBy teEn (3:0)    | Ι   | These input signals determine which of the 4 bytes of the current 32-bit data on HostTxData(31:0) lines are valid and are latched into the device on the rising edge of the HOST_CLK. See Section 4.11.1, Byte Alignment                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

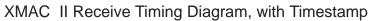

|           | TxPktValid         | Ι   | This input signal is asserted by the host to indicate that it has a frame for transmission. This signal must be asserted for the entire duration of a frame.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

|           | TxCRCDis able      | Ι   | If this input signal is asserted, then the XMAC II will not append CRC to the current frame that is being written into the transmit FIFO. This signal can be asserted anytime during TxPktValid.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

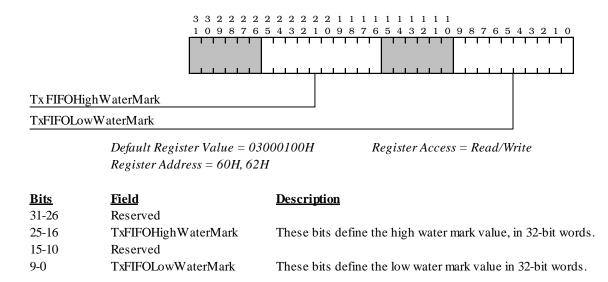

|           | TxFIFOA lmostEmpty | 0   | This output signal is asserted by the XMAC II to indicate that the number of bytes (to be transmitted) in the transmit FIFO is less than the value indicated by the <b>Transmit Low Water Mark Register</b> .                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

|           | TxFIFOA lmostFull  | 0   | This output signal is asserted by the XMAC II to indicate that the number of bytes (to be transmitted) in the transmit FIFO is more than the value indicated by the <b>Transmit High Water Mark Register</b> .                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

|           | FlushTxFIFO        | Ι   | The host can assert this input signal if the entire transmit FIFO needs to be flushed. $TxPktValid$ should be deasserted when this signal is asserted. Also, this signal should be asserted when $XmtPktError$ is asserted.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|           | FlushTxLastPkt     | Ι   | The host can assert this input signal (during a frame transfer) to flush the frame. If this signal is asserted after the frame transfer is complete, then there is no effect. This signal should be asserted only after transferring 8 32-bit words into the transmit FIFO.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|           | TxTranspMode       | Ι   | The host asserts this input signal whenever the XMAC II transmitter needs to be configured for transparent mode operation. See Section 4.18, Transparent Mode.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

|           | XmtPausePkt        | I   | The host asserts this input signal to generate a pre-programmed PAUSE frame. Any frame in the transmission process at the time of asserting this signal will be completely transmitted before the PAUSE frame is generated. The destination address field of the PAUSE frame will be same as the content of the <b>Pause Destination Address Register</b> . The pause timer field of the PAUSE frame will be same as the content of the <b>Pause Timer Register</b> . The source address field of the PAUSE frame will be same as the content of the <b>Pause Timer Register</b> . The source address field of the PAUSE frame will be same as the contents of the <b>Station Address Register</b> . This signal should not be asserted in half-duplex mode. Assert this signal for one <i>NP_CLK</i> clock cycle to transmit one PAUSE frame. If the <i>ExtPauseGen</i> (Bit #25) in the <b>Mode</b> register is set, then during the rising edge of this signal a non-zero PAUSE frame will be sent and during the falling edge of this signal a PAUSE frame with a zero timer value will be sent out. <i>For more information, refer to Section 4.9.2 Flow Control.</i> |

| Interface | Signal              | I/O | Signal Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

|-----------|---------------------|-----|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Host (Tx) | XmtPktError         | 0   | <ul> <li>This output signal is asserted by the XMAC II to indicate that an error condition occurred. The entire transmit FIFO must be flushed before transmission can continue. This signal stays asserted until the transmit FIFO flush is complete. Typically, this output signal is connected to <i>FlushTxFIFO</i> input signal. The potential error conditions are: <ul> <li>Excessive number of collisions</li> <li>Late collision</li> <li>Excessive deferral</li> <li>Tx FIFO underrun</li> </ul> </li> </ul> |

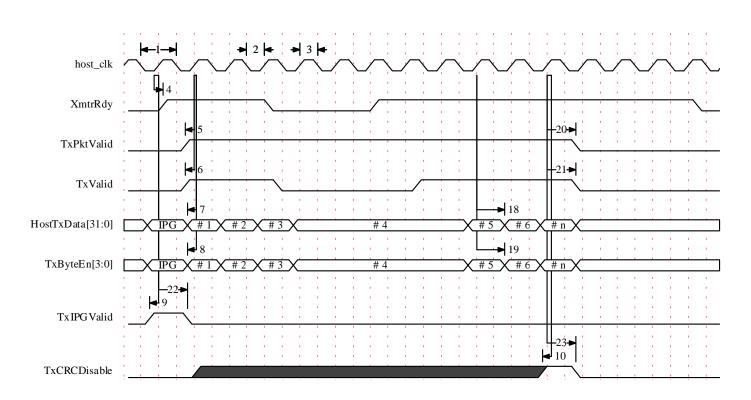

|           | TxIPGValid          | Ι   | If the host asserts this signal, then the least significant 8 bits of the first 32-bit word on <i>HostTxData</i> (31:0) lines represents the IPG value. This can be used to control the IPG value between frames. <i>See Section 4.16, Programmable IPG Control</i> .                                                                                                                                                                                                                                                 |

|           | XmtrRdy             | 0   | This signal indicates that the transmit FIFO is ready to accept data from the host.<br>The host should check this signal before transferring any data into the transmit<br>FIFO. See also Section 4.9.3 Transmit FIFO operation.                                                                                                                                                                                                                                                                                      |

|           | TxValid             | Ι   | This input signal is asserted by the host to indicate to the XMAC II that there is valid data on <i>HostTxData(31:0)</i> lines.                                                                                                                                                                                                                                                                                                                                                                                       |

|           | ForceXmt            | Ι   | This pin can be used to perform flow control in half duplex mode. <i>Do <u>not</u> assert in Full Duplex mode. See Section 4.17, Force Transmit Function.</i>                                                                                                                                                                                                                                                                                                                                                         |

| Host (Rx) | HostRxData(31:0)    | 0   | These pins provide the 32 bit data that is clocked out by the receive FIFO on the rising edge of the <i>HOST_CLK</i> . <i>RxPktValid</i> , <i>RcvValid</i> & <i>HostRcvRdy</i> signals should also be active for data transfer. In 16-bit mode <i>HostRxData(31:16)</i> should be connected to V <sub>CC</sub> through individual resistors.                                                                                                                                                                          |

|           | RxByteEn(3:0)       | 0   | These output signals indicate which of the 4 bytes on <i>HostRxData(31:0)</i> pins are valid data. <i>See Section 4.11.2, Byte Alignment</i> .                                                                                                                                                                                                                                                                                                                                                                        |

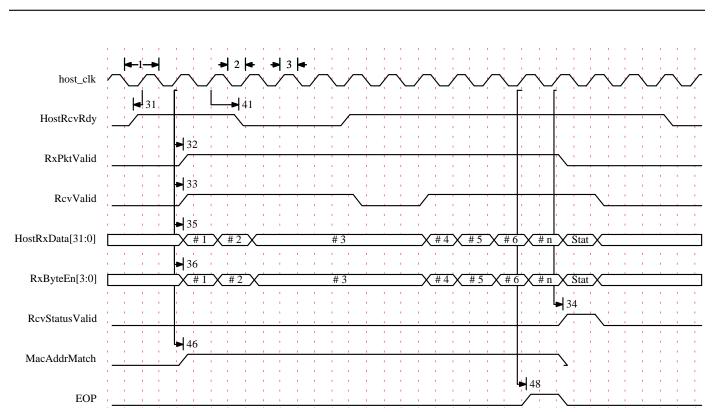

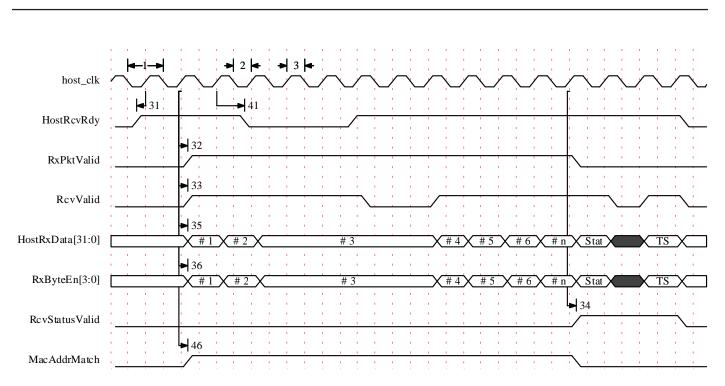

|           | RcvValid            | 0   | This output signal, when asserted indicates that the data on $HostRxData(31:0)$ pins are valid. This signal is asserted (for the first word) at the same time as $RxPktValid$ . Note that in between this signal may be asserted and deasserted.                                                                                                                                                                                                                                                                      |

|           | RxPkt Valid         | 0   | This output signal from the XMAC II defines the boundary (the beginning-to-the-<br>end-of-frame) of the incoming frame. This signal will be asserted when the XMAC<br>II is ready to transfer the first word of an incoming packet over the<br><i>HostRxData</i> (31:0) lines and will remain asserted until the last word of the incoming<br>packet is transferred. Note that this signal will be asserted even if the <i>HostRcvRdy</i>                                                                             |

|           | HostRcvRdy          | Ι   | This signal is asserted by the host to indicate that it is ready to accept data from the receive FIFO. Refer to description for <i>HostRxData</i> (31:0).                                                                                                                                                                                                                                                                                                                                                             |

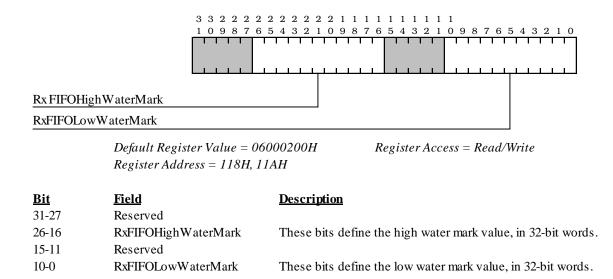

|           | RxFIFOA lmost Empty | 0   | This output signal is asserted by the XMAC II to indicate that the number of valid data words in the receive FIFO is less than the value indicated by the <b>Receive Low</b><br><b>Water Mark Register</b> . This signal will be de-asserted when the number of valid data words in the receive FIFO is more than the value indicated by the <b>Receive Low</b><br><b>Water Mark Register</b> .                                                                                                                       |

| Interface                      | Signal           | I/O | Signal Description                                                                                                                                                                                                                                                                                                                                                                                                                                      |

|--------------------------------|------------------|-----|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Host (Rx)                      | RxFIFOAlmostFull | 0   | This output signal is asserted by the XMAC II to indicate that the number of valid data words in the receive FIFO is more than the value indicated by the <b>Receive</b><br><b>High Water Mark Register</b> . This signal will be de-asserted when the number of valid data words in the receive FIFO is less than the value indicated by the <b>Receive</b><br><b>High Water Mark Register</b> .                                                       |

|                                | RxFIFOError      | 0   | This output signal will be asserted by the XMAC II whenever the receive FIFO overflows. This signal stays asserted as long as RxFIFO is not read or flushed.                                                                                                                                                                                                                                                                                            |

|                                | RxOutDis able    | Ι   | If this input signal is asserted by the host, then the XMAC II will tristate the <i>HostRxData(31:0) &amp; RxByteEn(3:0)</i> lines.                                                                                                                                                                                                                                                                                                                     |

|                                | FlushRxPkt       | Ι   | The host can assert this signal to request the XMAC II to flush the current packet that is being transferred from the receive FIFO to the host. Note that the FIFO will still output the data on the <i>HostRxData(31:0)</i> lines but <i>RcvValid</i> , <i>RxPktValid</i> signals will not be asserted. This pin can be used for external filtering. This signal should be asserted for at least one <i>HOST_CLK</i> cycle.                            |

|                                | FlushRxFIFO      | Ι   | The host asserts this signal to request the XMAC II to flush the entire receive FIFO. This signal should be asserted for at least one <i>HOST_CLK</i> cycle.                                                                                                                                                                                                                                                                                            |

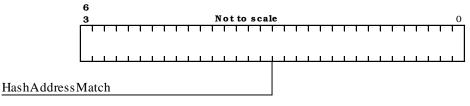

|                                | MACAddressMatch  | 0   | The XMAC II asserts this signal whenever the Destination address field of a packet that is being transferred from XMAC II to the Host matches the contents of the <b>Station Address Registers</b> or any of <b>Exact Match Registers</b> . This signal is asserted and deasserted with the <i>RxPktValid</i> signal.                                                                                                                                   |

|                                | RcvStatus Valid  | 0   | When this output signal is asserted by the XMAC II (after the last word of the current frame is clocked out of the receive FIFO), a valid status for the current frame is presented on the <i>HostRxData(31:0)</i> lines. If the <i>AppendTimeStamp bit</i> is set in the <b>Mode Register</b> , then this signal will be asserted for two clock cycles and the time stamp value is presented on <i>HostRxData(31:0)</i> lines during the second clock. |

| Node<br>Processor<br>Interface | NPDATA(31:0)     | I/O | These input/output data signals are used for accessing counters and registers. In 16-bit mode, unused pins $NPDATA(31:16)$ must be connected to V <sub>CC</sub> through a resistor.                                                                                                                                                                                                                                                                     |

|                                | NPADDR(8:0)      | Ι   | These input signals are used during registers/counters accesses. The address specifies which counter/register is being accessed for read/write operation. The input on these pins is a 16-bit word (not a byte address). In 32-bit mode, <i>NPADDR(0)</i> is not used.                                                                                                                                                                                  |

|                                | NPR/W            | Ι   | This input signal is used for selecting a read (or) write operation. This signal should be LOW for write operation and HIGH for read operation.                                                                                                                                                                                                                                                                                                         |

|                                | NPCS             | Ι   | This input signal must be asserted HIGH for read/write operations of counters and registers.                                                                                                                                                                                                                                                                                                                                                            |

|                                | NPRDY            | 0   | This output signal from the XMAC II (when asserted) indicates that the XMAC II has completed the current read/write operation.                                                                                                                                                                                                                                                                                                                          |

| Interface                      | Signal     | I/O | Signal Description                                                                                                                                                                                                                                                                                                                                                                                                                          |  |  |

|--------------------------------|------------|-----|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| Node<br>Processor<br>Interface | /NPINT     | 0   | This output signal is asserted (LOW) whenever one or more bits are set in the <b>Interrupt Status Register</b> and the corresponding bit(s) in the <b>Interrupt Mask Register</b> are cleared. This signal is deasserted when the <b>Interrupt Status</b> & the <b>Interrupt Event Registers</b> (which caused this signal to be asserted) are read. This is an Open Drain output signal and should be pulled up to Vcc through a resistor. |  |  |

| Control/<br>Clock<br>Interface | HOST_CLK   | Ι   | This input clock is used for clocking the data in and out of the transmit and receive FIFO. The rising edge is used for clocking. Valid <i>HOST_CLK</i> frequency is 33-66 MHz.                                                                                                                                                                                                                                                             |  |  |

|                                | REF_CLK    | Ι   | This input clock is used to derive other clocks required for the internal state machine operations. <i>REF_CLK</i> frequency is 125 MHz. This clock is also used to generate <i>GTX_CLK</i> .                                                                                                                                                                                                                                               |  |  |

|                                | NP_CLK     | Ι   | This input clock is used for register access. Valid NP_CLK frequency is 33-40MHz.                                                                                                                                                                                                                                                                                                                                                           |  |  |

|                                | TS_CLK     | Ι   | This input clock is used for time stamping the receive packets. The time stamp data (32-bits) will be available on the $HostRxData(31:0)$ lines. Note that the $RcvStatusValid$ signal will be asserted by the XMAC II when the time stamp data is valid. The valid range is $1 - 31.25$ MHz. External input (other than $31.25$ MHz) to this pin should be syncronized to $REF/4\_CLK$ .                                                   |  |  |

|                                | /TS_RESET  | Ι   | When the host asserts this signal, the XMAC II will reset the internal time stamp value to zero. The signal should be asserted for a minimum of one <i>TS_CLK</i> period                                                                                                                                                                                                                                                                    |  |  |

|                                | /RESET     | Ι   | This async input signal is used to initialize all XMAC II internal state machines, transmit & receive FIFOs, counters and registers. This should be asserted for a minimum of two <i>NP_CLK</i> periods.                                                                                                                                                                                                                                    |  |  |

|                                | TEST (2:0) | I/O | These input/output signals are used for testing purposes. These pins should be connected to GND.                                                                                                                                                                                                                                                                                                                                            |  |  |

|                                | REF/4_CLK  | 0   | This is a 31.25 MHz output clock provided by XMAC II. This could be used for <i>TS_CLK</i> .                                                                                                                                                                                                                                                                                                                                                |  |  |

|                                | Host16bits | Ι   | If this input signal is asserted, then the least significant 16 pins of the $HostTxData(31:0)$ & $HostRxData(31:0)$ pins will be used for host data transfer. (16-bit operation will be selected).                                                                                                                                                                                                                                          |  |  |

|                                | NP16bits   | Ι   | If this input signal is asserted, the least significant 16 pins of the <i>NPDATA(31:0)</i> 'pins will be used for register/counter access. (16-bit operation will be selected)                                                                                                                                                                                                                                                              |  |  |

|                                | GPInput    | Ι   | If this input pin is asserted, then XMAC II will set <i>Bit 0</i> of <b>General Purpose Port</b><br><b>Register</b> . This bit will remain set as long as this pin stays asserted.<br><i>This is an async. Input signal and must be valid for at least 40 nsec.</i>                                                                                                                                                                         |  |  |

| PHY<br>Interface               | TXD(7:0)   | 0   | These signals are the GMII Transmit Data signals. These signals are driven by the XMAC II and the data is synchronized with TCLK.                                                                                                                                                                                                                                                                                                           |  |  |

| GMII<br>Mode                   | TCLK       | 0   | This clock (125 MHz) is provided by XMAC II                                                                                                                                                                                                                                                                                                                                                                                                 |  |  |

| IVER C                         | TX_EN      | 0   | This signal is asserted by XMACII when data is present on the the TXD(7:0) lines.<br>This signal is synchronized with the TCLK.                                                                                                                                                                                                                                                                                                             |  |  |

| Interface        | Signal         | I/O | Signal Description                                                                                                                                                                                                                                                                                                                                                          |

|------------------|----------------|-----|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| PHY<br>Interface | TX_ER          | 0   | This signal is asserted by XMACII if it detects any error. This signal is synchronized with the TCLK.                                                                                                                                                                                                                                                                       |

| GMII<br>Mode     | RXD(7:0)       | Ι   | These signals are the GMII Receive Data signals. These signals are driven by the PHY device and the data is synchronized with RCLK.                                                                                                                                                                                                                                         |

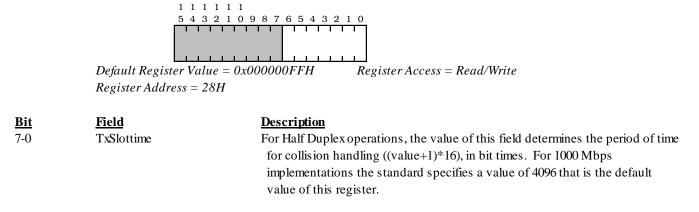

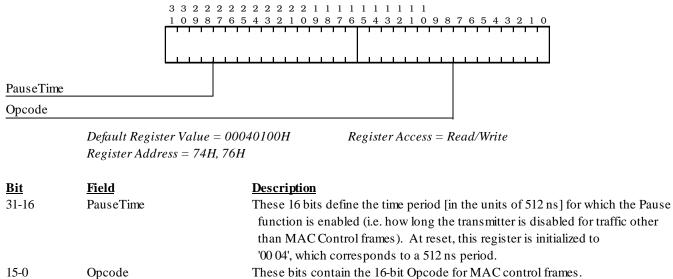

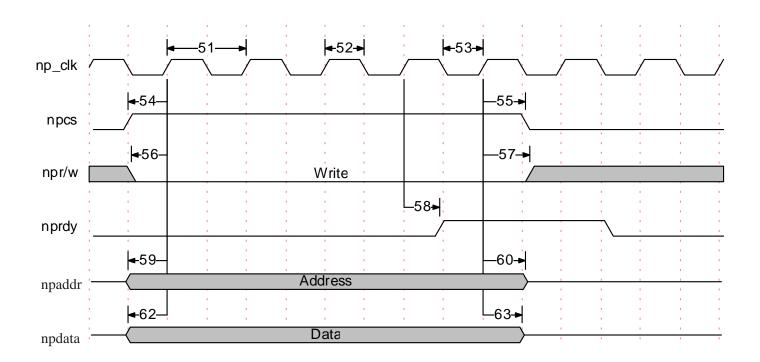

|                  | RCLK           | Ι   | This clock (125 MHz) is provided by the PHY device.                                                                                                                                                                                                                                                                                                                         |